¿Qué son PAL y PLA, Diseño y Diferencias?

Previamente, el diseño de circuitos lógicos se puede hacer usando SSI (Integración a pequeña escala) componentes como puertas lógicas, multiplexores, demultiplexores, FF, etc. Pero ahora un PLD puede reemplazar todos estos componentes SSI. Por lo tanto, esta es la razón por la cual la industria de SSI se está reduciendo en comparación con PLD, y estos se utilizan en varias aplicaciones. los dispositivo lógico programable o PLD es un tipo de chip utilizado para implementar el circuito lógico. Incluye un conjunto de elementos de circuitos lógicos que se pueden modificar de varias maneras. Un PLD parece una caja negra formada por interruptores programables y puertas lógicas. La función principal de los interruptores es permitir que las puertas lógicas dentro del PLD se asocien entre sí para realizar circuitos lógicos. Los PLD se clasifican en diferentes tipos, como SPLD-PLD simple (PLA y PAL), complejo CPLD-PLD, Arreglos de puertas programables de campo FPGA. Este artículo explica qué es un PAL y un PLA, el diseño y sus diferencias.

¿Qué son PAL y PLA?

Los dos Lógica de red programable y Placa lógica programable son tipos de PLDs (Dispositivos Lógicos Programables), y estos se utilizan principalmente para diseñar lógica de combinación entre sí por lógica secuencial. La principal diferencia entre estos dos es que PAL se puede diseñar con una colección de puertas AND y una colección fija de puertas OR, mientras que PLA se puede diseñar con una matriz programable de AND a través de una colección fija de puertas OR. Un dispositivo lógico programable ofrece un diseño de circuito lógico simple y flexible.

Antes de los dispositivos lógicos programables, el circuitos logicos combinatorios pueden diseñarse con multiplexores, y estos circuitos eran tanto rígidos como compuestos, y luego se desarrollan los PLD. El dispositivo lógico programable inicial fue la ROM, pero no tuvo éxito debido a los problemas de desperdicio de hardware además de mejorar el crecimiento exponencial de cada aplicación de hardware. Para superar este problema, se utilizaron PAL y PLA. Ambos son programables y usan el hardware de manera eficiente.

Diseño de lógica de red programable (PAL)

los definición del término PAL o Programmable Array Logic es un tipo de PLD conocido como circuito de dispositivo lógico programable, y el funcionamiento de este PAL es el mismo que el PLA. El diseño de lógica de red programable se puede realizar con puertas OR fijas y puertas AND programables. Usando esto, podemos implementar dos funciones simples siempre que las puertas AND asociadas con cada puerta OR denoten el mayor número de condiciones del producto que se pueden producir como SOP (suma del producto) de una función exacta.

Como las puertas lógicas como AND están continuamente conectadas a las puertas OR, indica que el producto del término del producto no se distribuye con las funciones de salida. La idea principal detrás del desarrollo de PLD es fabricar lógica booleana compuesta en un solo chip eliminando el cableado defectuoso, evitando el diseño lógico y reduciendo el consumo de energía.

Ejemplo de PAL

Implemente lo siguiente expresión booleana con la ayuda de lógica de matriz programable (PAL)

X=AB+AC'

Y = AB' + BC'

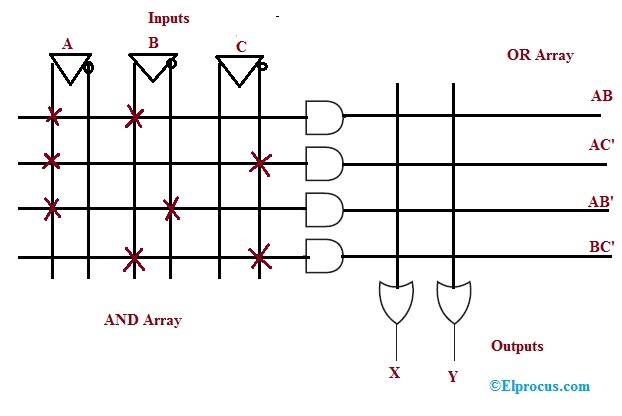

Las dos funciones booleanas anteriores tienen la forma de SOP (suma de productos). Los términos producto presentes en las expresiones booleanas son X e Y, y un término producto que es AC' es común a cada ecuación. Entonces, el número total de puertas lógicas requeridas para generar las dos ecuaciones anteriores es Y puertas-4 O puertas programables-2. El diagrama lógico PAL equivalente se muestra a continuación.

Las compuertas AND que son programables tienen derecho de entrada tanto para entradas variables normales como complementadas. En el diagrama lógico anterior, las entradas disponibles para cada puerta AND son A, A', B, B', C, C'. Entonces, para generar un término de producto único con cada puerta AND, se requiere el programa.

Todos los términos del producto se pueden obtener en las entradas de cada puerta OR. Aquí, las conexiones programables en la puerta lógica se pueden indicar con el símbolo 'X'.

Aquí las entradas de la puerta OR son fijas. Por lo tanto, los términos del producto requeridos están asociados con cada entrada de puerta OR. Como resultado, estas puertas generarán ecuaciones booleanas particulares. los '.' El símbolo representa conexiones permanentes.

Diseño de una matriz lógica programable (PLA)

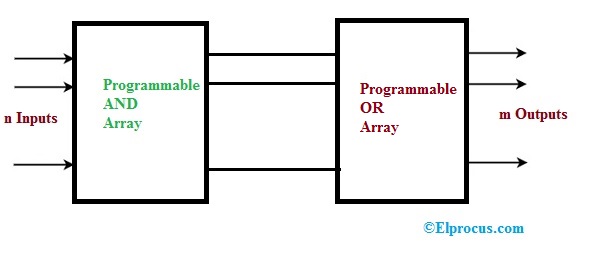

La definición del término PLA presenta la función booleana como una suma de productos (SOP). El diseño de esta matriz lógica programable se puede realizar utilizando puertas lógicas como AND, OR y NOT fabricando en chip, lo que logra cada entrada así como su complemento para cada puerta AND.

La salida de una puerta AND cada uno está conectada a la puerta OR cada uno. Finalmente, la salida de la puerta OR genera la salida del chip. Así es como se completa una asociación adecuada para utilizar las expresiones producto suma. En la red lógica programable, las conexiones de las puertas lógicas como AND & OR son programables. PLA es caro y difícil de comparar con PAL. El PAL usa dos métodos desarrollados diferentes que se pueden usar para una matriz lógica programable para mejorar la simplicidad de la programación. En este tipo de método, cada conexión puede hacerse usando un fusible en cada punto de intersección donde las conexiones innecesarias pueden aflojarse por la fusión del fusible. La técnica final consiste en realizar la conexión durante el proceso de fabricación utilizando la cobertura adecuada que se ofrece para el diseño de interconexión específico.

Ejemplo de APL

Implemente la siguiente expresión booleana usando una matriz lógica programable (PLA)

X = AB + AC'

Y = AB' + BC + AC'

Las dos funciones booleanas anteriores tienen la forma de SOP (suma de productos). Los términos producto presentes en las expresiones booleanas son X e Y, y un término producto que es AC' es común a cada ecuación. Entonces, el número total de puertas lógicas requeridas para generar las dos ecuaciones anteriores es AND gates-4, OR programable OR gates-2. El diagrama lógico PLA equivalente se muestra a continuación.

Las compuertas AND que son programables tienen derecho de entrada tanto para entradas variables normales como complementadas. En el diagrama lógico anterior, las entradas disponibles para cada puerta AND son A, A', B, B', C, C'. Entonces, para generar un término de producto único con cada puerta AND, se requiere el programa.

Todos los términos del producto se pueden obtener en las entradas de cada puerta OR. Aquí, las conexiones programables en la puerta lógica se pueden indicar con el símbolo 'X'.

Diferencia entre PAL y PLA

los Diferencia entre PAL y PLA en forma tabular incluye principalmente Formulario PAL y PLA completoconstrucción, disponibilidad, flexibilidad, costo, número de funciones y velocidad que se analizan a continuación.

| Lógica de red programable (PAL) | Matriz Lógica Programable (PLA) |

| La forma completa de PAL es lógica de matriz programable | La forma completa de PLA es una matriz lógica programable |

| La construcción de PAL se puede hacer usando la colección programable de puertas AND & OR | La construcción de PLA se puede realizar utilizando la colección programable de puertas AND y la colección fija de puertas OR. |

| La disponibilidad de PAL es menos prolífica | La disponibilidad de PLA es Más |

| La flexibilidad de la programación PAL es más | La flexibilidad del PLA es menor |

| El costo de un PAL es caro | El costo del PLA es promedio |

| El número de funciones implementadas en PAL es significativo | El número de funciones implementadas en PLA es limitado |

| La velocidad de PAL es lenta | La velocidad del PLA es alta. |

Es por tanto PAL y PLA. De la información anterior, finalmente, podemos concluir que son los Dispositivos Lógicos Programables (PLDs) donde el matriz lógica programable es más flexible que la lógica matricial programable. Pero, la lógica de matriz programable puede generar sin esfuerzo un circuito lógico combinatorio. Aquí hay una pregunta para usted, ¿cuál es el papel de PAL y PLA en electrónica digital?

Si quieres conocer otros artículos parecidos a ¿Qué son PAL y PLA, Diseño y Diferencias? puedes visitar la categoría Generalidades.

Deja una respuesta

¡Más Contenido!