Qué es el codificador prioritario : Funcionamiento y sus aplicaciones

En Electrónica Digital, los codificadores binarios son los circuitos lógicos combinacionales de múltiples entradas, que consideran todas las líneas de entrada simultáneamente y luego las convierten en una única salida codificada equivalente. Un codificador digital de n bits contiene 2^n líneas de entrada y n líneas de salida. Para superar las desventajas de los codificadores binarios, se desarrollaron codificadores de prioridad que funcionan en base a la entrada de mayor prioridad. En este artículo se describe brevemente un codificador de prioridad y sus aplicaciones.

¿Qué es un codificador de prioridad?

El codificador de prioridad es un circuito lógico combinacional que contiene 2^n líneas de entrada y n líneas de salida y representa la entrada de mayor prioridad entre todas las líneas de entrada. Cuando varias líneas de entrada están activas en alto al mismo tiempo, la entrada que tiene la mayor prioridad se considera la primera en generar la salida.

Se utiliza para resolver los problemas de los codificadores binarios, que generan una salida errónea cuando más de una línea de entrada está activa en alto. Si más de una línea de entrada está activa (1) al mismo tiempo, este codificador prioriza cada nivel de entrada y asigna el nivel de prioridad a cada entrada.

La salida de este codificador corresponde a la entrada que tiene la mayor prioridad. Para obtener la salida, sólo se tiene en cuenta la entrada con mayor prioridad, ignorando todas las demás líneas de entrada. Se trata de un tipo de codificador binario o de un codificador ordinario con función de prioridad. La entrada que tiene la mayor magnitud o la mayor prioridad se codifica primero en lugar de otras líneas de entrada. Por tanto, la salida generada se basa en la prioridad asignada a las entradas.

En la mayoría de las aplicaciones digitales, estos codificadores se utilizan para seleccionar las entradas que tienen el mayor nivel de prioridad. Este proceso de selección de la entrada se llama arbitraje. Por ejemplo, cuando varios dispositivos transmiten los datos a través de los sistemas informáticos, este codificador habilita el dispositivo que tiene la mayor prioridad y permite el acceso al ordenador entre todos los demás dispositivos, que tienen una prioridad menor.

Estos codificadores están diseñados con 4 entradas y 8 entradas. El codificador de prioridad de 4 bits contiene 4 entradas y 2 salidas junto con una salida válida. El codificador de prioridad de 8 bits contiene 8 entradas y 3 salidas. El circuito del codificador de prioridad con la tabla de verdad para 8 bits y 4 bits se explica en la sección siguiente.

codificador de prioridad de 8 a 3

Este tipo de codificador también se denomina codificador de prioridad de 8 bits o de octal a binario. Este tipo de codificador consta de 8 entradas y 3 salidas. Cuando varias entradas están activas al mismo tiempo, se considera que la entrada con mayor prioridad representa la salida.

Por ejemplo, si las entradas D1, D2 y D3 están activas en alto o en 1 lógico, independientemente de los demás bits de entrada, la salida codificada del codificador de prioridad será D3, es decir, 111. En este caso, los bits de entrada D1, y D2 son condiciones irrelevantes o de despreocupación.

La tabla de verdad del codificador de prioridad de 8 a 3 se muestra a continuación.

|

D7 |

D6 | D5 | D4 | D3 | D2 | D1 | D0 | A | B |

C |

|

0 |

0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

|

0 |

0 | 0 | 0 | 0 | 0 | 1 | X | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 1 | X | X | 0 | 1 |

0 |

| 0 | 0 | 0 | 0 | 1 | X | X | X | 0 | 1 |

1 |

|

0 |

0 | 0 | 1 | X | X | X | X | 1 | 0 | 0 |

| 0 | 0 | 1 | X | X | X | X | X | 1 | 0 |

1 |

|

0 |

1 | X | X | X | X | X | X | 1 | 1 | 0 |

| 1 | X | X | X | X | X | X | X | 1 | 1 |

1 |

De la tabla de verdad anterior, podemos observar que D0, D1, D2, D3, D4, D5, D6, D7 son las entradas, y A, B, C son las salidas de un codificador de prioridad 8 a 3.

La salida "A" de un codificador prioritario se representa como activa alta o lógica "1" sólo cuando las entradas D4, D5, D6 y D7 están activas altas. La salida "B" de un codificador está en 1 lógico sólo cuando las entradas D2, D3, D6 y D7 están activas en alto. Del mismo modo, la salida "C" se representa como "1" lógico sólo cuando las entradas D1, D3, D5 y D7 están activas en alto.

Las expresiones de salida para A, B y C se escriben a partir de la simplificación del mapa de Karnaugh (mapa K) o de la tabla de verdad.

Las expresiones de salida se obtienen como se muestra a continuación,

A = D4+D5+D6+D7

B = D2+D3+D6+D7

C = D1+D3+D5+D7

A partir de estas expresiones simplificadas, el diagrama del circuito del codificador de prioridad 8 a 3 se dibuja con puertas lógicas como se muestra en la figura siguiente.

los tipos de 8 a 3 están disponibles en el CI estándar 74LS148, que consta de 8 entradas activas bajas o lógicas 0 y 3 bits de salida activos altos o lógicos 1. Las diferentes propiedades de este tipo de codificador incluyen la codificación en cascada de n bits para la codificación prioritaria, la codificación de las entradas de mayor prioridad, las conversiones de código, la conversión de decimal a BCD, para habilitar la línea de salida con activo bajo cuando todas las líneas de entrada son activas altas.

codificador de prioridad de 4 a 2

También se denomina prioridad de 4 bits, y consta de 4 líneas de entrada y 2 de salida. Como un codificador contiene 2^n líneas de entrada y n líneas de salida. La tercera salida es "V", que se considera un indicador de pero válido y se pone a 1 cuando más de una línea de entrada está alta o activa (1).

Si el bit válido es igual a "0", entonces todas las entradas son "0". En este caso, las otras 2 líneas de salida se consideran como condiciones de despreocupación denotadas por "X

El tabla de verdad de un codificador de prioridad 4 a 2 se muestra a continuación.

| D3 | D2 | D1 | D0 | A | B |

V |

|

0 |

0 | 0 | 0 | X | X | 0 |

|

1 |

0 | 0 | 0 | 0 | 0 | 1 |

|

X |

1 | 0 | 0 | 0 | 1 |

1 |

| X | X | 1 | 0 | 1 | 0 |

1 |

| X | X | X | 1 | 1 | 1 |

1 |

De la tabla de verdad anterior, podemos observar que D3, D2, D1, D0 son las entradas; A y B son las salidas y V es el indicador de bit válido. Aquí la entrada D3 es la de mayor prioridad y D0 es la de menor prioridad.

Cuando la entrada D3 está activa en alto (1), que tiene la mayor prioridad independientemente de todas las demás líneas de entrada, la salida del codificador de 4 bits de prioridad es 11.

Cuando la entrada D3 es activa baja y la D2 es activa alta, que tiene la siguiente prioridad más alta con independencia de todas las demás líneas de entrada, entonces la salida es BA=10.

Cuando las entradas D3, D2 están activas bajas, y la D1 está activa alta y tiene la siguiente prioridad más alta independientemente de la línea de entrada restante, entonces la salida será BA = 01

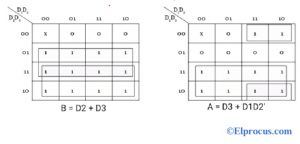

La expresión de salida puede determinarse para un codificador de 4 bits con la ayuda de un mapa de karnaugh (mapa K), como se muestra a continuación.

A = D3 + D1D2′

B= D2 + D3

V = D0 + D1 + D2 + D3

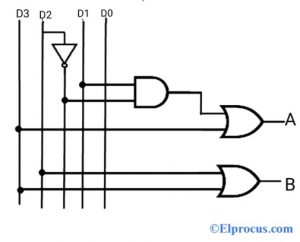

A partir del mapa K anterior, se obtienen las expresiones simplificadas de las salidas A y B. A partir de estas expresiones de salida, el esquema del circuito del codificador de prioridad 4 a 2 se ilustra con puertas lógicas como se muestra a continuación.

El diagrama del circuito del codificador de prioridad de 4 a 2 se dibuja con 2 puertas OR, y la combinación de la puerta AND y la puerta NOT representan el bit válido, que se utiliza cuando más de una entrada es lógicamente alta (1). Así, se codifican cuatro entradas con dos salidas en función de la prioridad asignada a las entradas

Código Verilog

La salida del codificador es imprecisa cuando se asigna más de una línea de entrada con lógica 1. Sólo funciona cuando una de las entradas es alta (1). Por lo tanto, el codificador no funciona con varias líneas de entrada altas. Para superar este inconveniente, se prioriza el nivel de cada entrada. Por tanto, en el caso de múltiples líneas de entrada, la salida del codificador corresponde a la entrada designada con la mayor prioridad. Esto se llama codificador de prioridad.

En el estilo estructural, el código Verilog del codificador de prioridad se escribe como se muestra a continuación.

módulo or_gate (C, A, B);

entrada A, B;

salida C;

asigna C= A|B;

endmodule;

módulo not_gate (F, E);

entrada E;

salida F;

asignar F=-E;

endmodule;

módulo y_puerta(Z, X, Y) ;

entrada X, Y;

salida Z;

asigna Z= X&Y;

endmodule;

módulo estructura_codificadora_prioritaria(A0, A1, Y0, Y1, Y2, Y3);

entrada Y0, Y1, Y2, Y3;

salida A0, A1;

not_gate U1(.F(Y2bar), . e(Y2) ) ;

and_gate U2(.Z(W1) ,. X(Y2bar), . Y(Y1)) ;

o_gate (.C(A1), . A(Y3), . B(Y2)) ;

o_puerta(.C(A0),. A(Y1),. B(W1)) ;

endmodule;

Diferencia entre codificador y codificador de prioridad

La principal diferencia entre el codificador y el codificador de prioridad es que el codificador genera una salida de error cuando más de una entrada es alta. Pero se utilizan en aplicaciones que comprimen datos. De ahí que se introduzcan los codificadores prioritarios para superar los problemas de los codificadores binarios.

El codificador de prioridad genera la salida precisa considerando la entrada de mayor prioridad entre las múltiples líneas de entrada. Pueden gestionar las solicitudes de interrupción de un microprocesador detectando la interrupción de mayor prioridad.

Si un circuito contiene múltiples entradas, se utiliza para reducir el número de cables necesarios durante el diseño

Aplicaciones

Algunas de las aplicaciones del codificador de prioridad son,

- Se utiliza para reducir el número de cables y conexiones necesarias para el diseño de circuitos electrónicos que tienen varias líneas de entrada. Por ejemplo, los teclados.

- Se utiliza para controlar la posición en la navegación del barco y la posición del brazo robótico.

- Se utiliza en la detección de la entrada de mayor prioridad en diversas aplicaciones de los controladores de interrupción del microprocesador.

- Se utiliza para proteger toda la red de los piratas informáticos transmitiendo el código binario a través de la red.

- Se utiliza para codificar la salida del convertidor analógico-digital.

- Se utiliza en la sincronización de la velocidad de los motores en las industrias.

- Vehículos robotizados usados

- Utilizados en aplicaciones de sistemas de domótica con RF

- Utilizado en hospitales para sistemas de monitorización de la salud

- Utilizado en sistemas de comunicación segura con tecnología de radiofrecuencia para permitir el código secreto.

Por tanto, se trata de una visión general del Codificador de Prioridades definición, diagrama del circuito del codificador de prioridad 4 a 2 y 4 a 3, diagrama del circuito del codificador de prioridad 8 a 3, código Verilog y aplicaciones. Aquí tienes una pregunta: "¿Cuáles son las diferencias entre codificadores y multiplexores?"

Si quieres conocer otros artículos parecidos a Qué es el codificador prioritario : Funcionamiento y sus aplicaciones puedes visitar la categoría Generalidades.

Deja una respuesta

¡Más Contenido!