Permitir una sólida monitorización por cable basada en el estado para la Industria 4.0-Parte 2

Introducción

En la primera parte de este artículo, "Enabling Robust Wired Condition Monitoring for Industry 4.0-Part 1", presentamos las soluciones de interfaz por cable de Analog Devices, que reducen el ciclo de diseño y el tiempo de prueba del cliente, y permiten una comercialización más rápida de las soluciones industriales de CbM. Se debatieron varios aspectos, como la selección de un acelerómetro MEMS y una capa física adecuados, así como el rendimiento de la CEM y el diseño de la fuente de alimentación. Además, en la Parte 1 se presentaron tres soluciones de diseño y compensaciones de rendimiento. Este artículo (Parte 2 de 2) se centra en las consideraciones detalladas del diseño de la capa física para las soluciones de diseño de SPI a RS-485/RS-422 presentadas en la Parte 1.

Entre los retos más comunes a la hora de implementar una interfaz de capa física cableada para MEMS se encuentran la gestión de la solidez de la EMC y la integridad de los datos. Sin embargo, extender una interfaz sincronizada con el reloj, como la SPI, a través de largos cables RS-485/RS-422, así como combinar la alimentación y los datos a través de los mismos cables de par trenzado (alimentación fantasma), presenta varios retos adicionales. Este documento analiza las siguientes consideraciones clave y ofrece recomendaciones para el diseño de la interfaz de la capa física:

- Gestionar la sincronización horaria del sistema

- Recomendaciones sobre la velocidad de datos frente a la longitud del cable

- Diseño y simulación de filtros para arquitecturas de potencia y datos compartidos

- Compensaciones de rendimiento de los componentes pasivos para la implementación de la potencia fantasma

- Ventana de selección de componentes y diseño del sistema

- Mediciones experimentales

Sincronización horaria y longitud del cable

Al diseñar un enlace SPI a RS-485/RS-422, el cable y los componentes afectan a la sincronización del reloj y los datos del sistema. En un cable largo, la señal SCLK experimentará un retardo de propagación en el cable, de aproximadamente 400 ns a 500 ns para un cable de 100 metros. Para una transferencia de datos MOSI, las señales MOSI y SCLK también se retrasan por el cable. Sin embargo, los datos enviados desde el esclavo MISO al maestro estarán desincronizados con el SCLK en el doble del retardo de propagación del cable. El máximo SCLK SPI posible está definido por el retardo de propagación del sistema, que incluye el retardo de propagación del cable y los retrasos de propagación de los componentes maestro y esclavo.

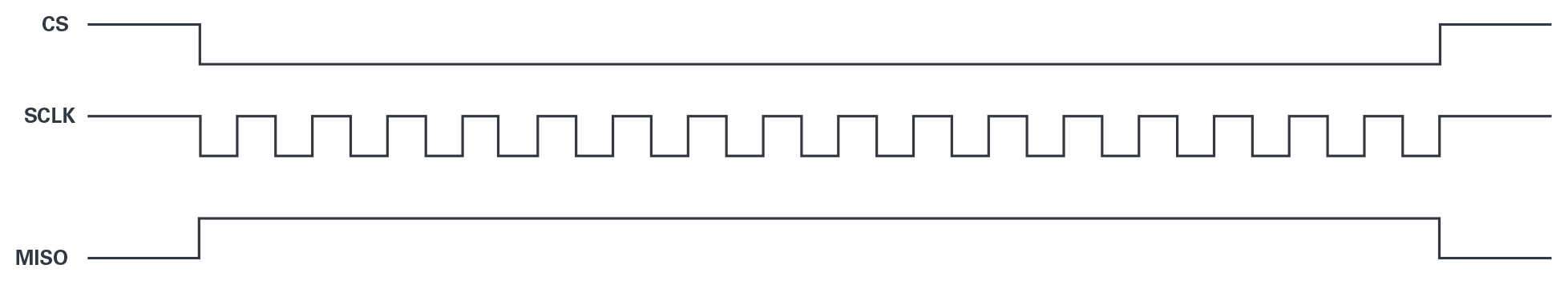

La figura 1 ilustra cómo el retardo de propagación del sistema puede dar lugar a un muestreo inexacto de la SPI MISO en el maestro SPI. En un sistema sin cable RS-485/RS-422, los datos MISO y el SCLK SPI se sincronizarán con poco o ningún retraso. En un sistema con cable, los datos MISO del esclavo SPI están desincronizados con el SCLK SPI por un retardo de propagación del sistema, señalado como tpd1 en la Figura 1. Los datos MISO vuelven al maestro desincronizados por dos retrasos de propagación del sistema, denominados tpd2. Como los datos se desplazan hacia la derecha debido a los retrasos de propagación de los cables y componentes, el muestreo de datos es inexacto.

Figura 1: Sincronización de los datos MISO y SCLK SPI para un sistema con y sin cable largo RS-485/RS-422.

Para evitar un muestreo MISO inexacto, se puede reducir la longitud del cable, disminuir el SCLK SPI o implementar un esquema de compensación del SCLK SPI (desplazamiento de la fase del reloj) en el controlador maestro. Teóricamente, el retardo de propagación del sistema debe ser inferior al 50% del periodo del reloj SCLK para una comunicación sin errores, y en la práctica se puede utilizar como regla general un límite de retardo del sistema del 40% del SCLK.

La Figura 2 proporciona una orientación sobre el SCLK SPI frente a la longitud del cable para los dos diseños de SPI a RS-485/RS-422 descritos en la Parte 1.1 El diseño no aislado utiliza los dispositivos RS-485/RS-422 de alta velocidad, resistentes a la compatibilidad electromagnética y de tamaño reducido de Analog Devices (ADM3066E y ADM4168E). El diseño aislado también incluye el iCoupler de Analog Devices® el dispositivo ADuM5401 con aislamiento de señal y potencia, que proporciona una robustez adicional de EMC e inmunidad al ruido para los enlaces SPI a RS-485/RS-422. Este diseño añade un retardo de propagación adicional al sistema, que limita el funcionamiento a velocidades de SCLK SPI más altas. En los tramos largos de cable (más de 30 m), se recomienda encarecidamente que se añada aislamiento para ayudar a mitigar los bucles de tierra y los eventos de compatibilidad electromagnética (EMC), como las descargas electrostáticas (ESD), los transitorios eléctricos rápidos (FET) y las sobretensiones de alta tensión acopladas al cableado de transmisión de datos. Cuando las longitudes de los cables alcanzan los 30 m o más, el rendimiento de SPI SCLK en relación con la longitud del cable del diseño aislado en comparación con el diseño no aislado es similar, como se muestra en la Figura 2.

Figura 2. Pautas de longitud del cable SPI SCLK frente a la longitud del cable para diseños aislados y no aislados.

Potencia fantasma

Papel pintado

La alimentación fantasma combina la alimentación y los datos en un solo par trenzado, lo que permite una solución de 1 cable entre los dispositivos maestro y esclavo. La combinación de datos y energía en un solo cable proporciona una solución de conector único para los nodos de sensores periféricos con limitaciones de espacio.

La alimentación y los datos se distribuyen por un único par trenzado mediante una red de condensadores inductivos, como se muestra en la figura 3. Los datos de alta frecuencia se acoplan a las líneas de datos mediante condensadores en serie, que también protegen al transceptor RS-485/RS-422 de las tensiones de CC del bus, como se muestra en la Figura 3a. La figura 3 muestra una fuente de alimentación conectada al controlador maestro a través de un inductor conectado a una línea de datos. La fuente de alimentación de 5V DC polariza el bus de datos a AC, como se muestra en la Figura 3b. En la figura 3c, la trayectoria de la corriente está representada por IPWR entre el maestro y el esclavo, extrayendo la energía de la línea mediante un inductor en el nodo sensor esclavo de monitorización condicional (CbM) situado en el extremo del cable.

Figura 3: Niveles de tensión de CA y CC de la capa física de potencia fantasma.

Filtro paso alto

A efectos de este artículo, se supone que la red de inductores-capacitores de potencia fantasma se añade a dos cables, que llevan la conversión RS-485/RS-422 de la señal SPI MISO. La figura 4 muestra el diseño de maestro y esclavo SPI a RS-485/RS-422 y el circuito de filtro de potencia fantasma para la línea de datos SPI MISO. El circuito de filtrado es un filtro de paso alto y, por tanto, requiere que las señales de datos transmitidas no tengan contenido de CC ni frecuencias muy bajas.

Figura 4: Diseño de SPI a RS-485/RS-422 y circuito de filtro de potencia fantasma.

En la figura 5, que es una representación simplificada de la figura 4, se muestra un circuito de filtro paso alto de segundo orden. La salida de tensión en el dispositivo de transmisión RS-485/RS-422 se denomina VTXcon una impedancia de salida de R1 15 Ω. El R2 30 kΩ es una impedancia de entrada estándar para el dispositivo receptor RS-485/RS-422. Los valores del inductor (L) y del condensador (C) pueden seleccionarse en función de la velocidad de datos deseada del sistema.

Figura 5: Filtro paso alto de segundo orden para la ruta de datos de transmisión RS-422 y de recepción RS-485/RS-422.

Al seleccionar los valores del inductor (L) y del condensador (C), hay que tener en cuenta la caída de tensión máxima del bus RS-485/RS-422 y el tiempo de caída, como se muestra en la figura 6. Hay estándares, como el de Ethernet de par trenzado simple,2 que especifican el droop de tensión y el tiempo de droop máximos permitidos, como se muestra en la Figura 6a. En algunos sistemas, el droop de tensión permitido y el tiempo máximo de droop pueden ser mayores, limitados por el punto de cruce de la polaridad de la señal, como se muestra en la figura 6b

El droop de tensión y el tiempo de droop pueden utilizarse junto con una simulación de la figura 5 para determinar la frecuencia de paso alto del sistema.

Para un sistema bien amortiguado, la relación entre la frecuencia de corte del filtro de paso alto y el requisito de estatismo viene dada por la ecuación 1.3

Figura 6. Caída de tensión y caída de tiempo en el receptor RS-422.

Al añadir alimentación fantasma a un sistema de comunicación SPI a RS-485/RS-422, es evidente que la frecuencia mínima posible del SCLK SPI estará limitada por los componentes del filtro de alimentación fantasma.

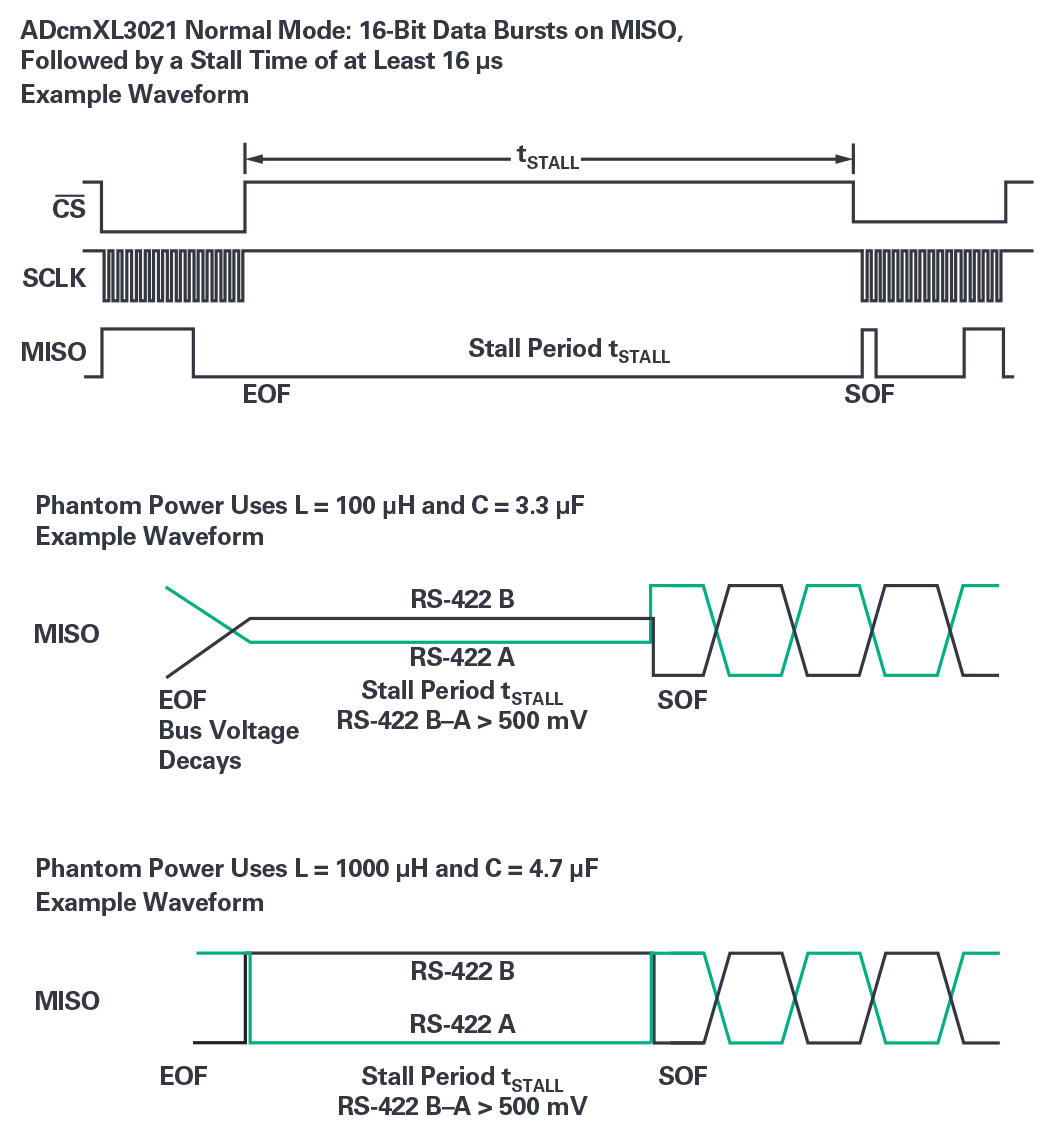

Para conseguir una comunicación fiable sin errores de bits, el SCLK SPI mínimo debe considerarse en el peor de los casos, por ejemplo, cuando todos los bits MISO muestreados del SPI están lógicamente altos, como se muestra en la Figura 7. Si todos los bits MISO muestreados son lógicamente altos, se obtiene una velocidad de bits inferior a la del SCLK SPI del sistema. Por ejemplo, si el SPI SCLK es de 2 MHz y los 16 bits son lógicamente altos, el conjunto de filtros LC de potencia fantasma verá una tasa de bits SPI MISO equivalente de 125 kHz.

Figura 7. Protocolo SPI con ráfaga MISO de 16 bits, todo lógico alto.

Como se menciona en el apartado "Sincronización temporal y longitud de los cables", las longitudes de cable más largas requieren tasas de SCLK SPI más bajas. Sin embargo, la potencia fantasma limita la tasa SCLK SPI más baja posible. Para equilibrar estos requisitos opuestos, los componentes de los filtros pasivos, en particular los inductores, deben ser cuidadosamente seleccionados y caracterizados.

Selección de componentes pasivos

A la hora de seleccionar un inductor de potencia adecuado, hay que tener en cuenta una serie de parámetros, como la inductancia suficiente, la tasa de corriente/saturación, la frecuencia autorresonante (SRF), la baja resistencia de CC (DCR) y el tamaño del paquete. La tabla 1 muestra una selección de inductancias de potencia y parámetros de interés.

La corriente nominal debe cumplir o superar los requisitos de corriente total del nodo sensor MEMS alimentado a distancia, y la corriente nominal de saturación debe ser mucho mayor.

El inductor no mostrará una alta impedancia a los datos de corriente alterna por encima de su SRF especificada, y en algún momento comenzará a tener una característica de impedancia capacitiva. El SRF del inductor elegido limitará el SCLK SPI máximo que se puede utilizar en la capa física SPI a RS-485/RS-422, como se muestra en la Tabla 1. Cuando se trabaja con cables largos, es posible que no se alcance la SRF del inductor; por ejemplo, no es posible alcanzar tasas de SCLK SPI de 11 MHz (SRF del número de pieza 744043101) en 10 m de cable. En otros casos, cuando se trabaja con cables largos, la SRF del inductor puede alcanzarse a velocidades SPI SCLK más bajas (2,4 MHz, 1,2 MHz). Como ya se ha dicho, cuando se utiliza en una red de filtro de potencia fantasma, un inductor también limitará la tasa SCLK al máximo.

Los inductores de mayor valor están disponibles en paquetes de 12,7 mm × 12,7 mm, mientras que los de menor valor están disponibles en paquetes de 4,8 mm × 4,8 mm.

La tabla 2 muestra que compensar los requisitos opuestos para minimizar el tamaño del inductor es difícil debido a las limitaciones físicas (devanados internos).

| Número de pieza | L (µH) | IRATÉ (mA) | Frecuencia autorresonante (SRF) (MHz) | Resistencia DC (DCR) (Ω) | Tamaño de la carcasa (mm) |

| 744043101 | 100 | 290 | 11 | 0.6 | 4.8 × 4.8 |

| LPS8045B-105 | 1000 | 230 | 1.3 | 3.22 | 8.0 × 8.0 |

| 76877530 | 1000 | 300 | 2.4 | 3.3 | 7.8 × 7.0 |

| SDR0805-102KL | 1000 | 210 | 3.0 | 4.5 | 7.8 × 7.8 |

| 7687714222 | 2200 | 260 | 1.2 | 6.5 | 10 × 10 |

| SRR1208-222KL | 2200 | 280 | 0.65 | 4.2 | 12.7 × 12.7 |

| Parámetro | Implicaciones para el tamaño de los paquetes |

| Inductancia suficientemente alta | Los valores de inductancia más elevados implican un mayor número de devanados internos y un mayor tamaño de la carcasa. |

| Un mayor factor de riesgo (SRF) | Un SRF más alto significa menos devanados internos y un tamaño más pequeño. |

| Mayor corriente nominal y de saturación | Menos bobinas internas, pero mayor tamaño de la carcasa. |

| Baja DCR | Para conseguir una DCR más baja, los cables deben ser más gruesos y tener menos bobinas. |

Las restricciones para seleccionar un condensador de bloqueo de CC adecuado se limitan a la capacidad de sobretensión transitoria y a la capacidad de tensión de CC. La tensión nominal de CC debe ser mayor que la tensión de polarización máxima del bus, como se muestra en la figura 3. En caso de cortocircuito en el cable o en el conector, las corrientes de inductancia estarán desequilibradas y serán disipadas por las resistencias de terminación. Los condensadores de bloqueo de CC deben estar dimensionados para los picos de tensión transitoria en caso de cortocircuito. Por ejemplo, en los sistemas de baja potencia con corrientes de saturación de los inductores de aproximadamente 1 A, el condensador de bloqueo de CC correspondiente debe tener un valor nominal de al menos 50 V de CC.4

Implantación del sistema

Ventana de diseño y selección de componentes

Al extender una interfaz sincronizada con el reloj, como la SPI, a través de largos cables RS-485/RS-422, así como al combinar la alimentación y los datos en los mismos cables de par trenzado (alimentación fantasma), la figura 8 resume las limitaciones de diseño mencionadas en este artículo. El SCLK SPI mínimo posible está definido por los componentes del filtro de potencia fantasma, que filtran en paso alto los datos de la línea de datos SPI. El máximo SCLK SPI se define por la frecuencia autorresonante (SRF) del inductor de potencia fantasma o por el retardo de propagación del sistema (el que sea menor).

Figura 8. Limitaciones de la ventana de diseño.

La Tabla 3 proporciona los valores sugeridos de inductancia y capacitancia, y el correspondiente SPI SCLK mínimo determinado mediante la simulación de la Figura 5 y utilizando la Figura 6 y la Ecuación 1 como guía. Esto supone que VDROOP es el 99% de VPEAK. Este SCLK SPI mínimo también tiene en cuenta el peor de los casos, como se describe en la Figura 7, en el que todos los bits de una ráfaga de datos son lógicamente altos. La longitud del cable correspondiente se estima mediante la figura 2. El máximo SCLK SPI se define por el retardo de propagación del sistema o por el valor SRF del inductor

Aquí tienes un ejemplo de cálculo.

Para determinar el máximo SCLK SPI :

- Especifica la longitud de cable necesaria para el sistema. Para este ejemplo, elegiremos 10 m de cable RS-485/RS-422.

- Utiliza la Figura 2 para determinar el máximo SCLK SPI posible para el sistema. Para 10 m de cable, esto corresponde a aproximadamente 2,6 MHz de SPI SCLK. Deduciendo el máximo SPI SCLK en un 10% para tener en cuenta las tolerancias de los componentes de la LC, se obtiene un SPI SCLK de 2,3 MHz. El máximo SCLK SPI posible también puede estar limitado por el SRF del inductor elegido

Para determinar el SCLK SPI mínimo:

- Considera un protocolo SPI en el que todos los bits de la línea MISO están lógicamente en alto. Para este ejemplo, elegiremos un protocolo SPI de 16 bits, en el que se muestrearán 16 bits de datos SPI MISO durante 32 transiciones SCLK. Si los 16 bits son lógicamente altos, la velocidad de bits efectiva es de 2,3 MHz / 32 = 72 kHz.

- Utilizando la figura 5 con una onda cuadrada de 72 kHz en VTXla forma de onda de la tensión en el extremo del cable VRX se puede simular para diversos valores de L y C. A medida que aumenta la longitud del cable, aumenta el valor del inductor y el tamaño del paquete del inductor. El valor de la capacidad también aumenta.

- La selección de los valores L y C es subjetiva y depende de los ajustes de estatismo deseados, como se describe en la figura 6. Para este ejemplo, supondremos que VDROOP = VPEAK × 99%.

- Utilizando inductores de 100 µH y condensadores de 3,3 µF y una onda cuadrada de 72 kHz en VTX da un TDROOP de 7 µs, donde VDROOP = VPEAK × 99%.

- A TDROOP de 6 µs a 7 µs equivale a un SCLK SPI de 2,3 MHz a 2,6 MHz.

- Si eliges una inductancia de 100 µH (744043101), un SCLK SPI de 2,6 MHz es inferior al SRF de la inductancia de 11 MHz.

El uso de inductores de 100 µH y condensadores de 3,3 µF proporciona la menor superficie de placa de componentes. Si utilizas inductores más grandes, como 1000 µH o 2200 µH, la superficie de la placa de componentes puede triplicarse. El máximo SPI SCLK teórico está definido por la SRF del inductor, que en la práctica puede no ser posible, por ejemplo a 11 MHz utilizando el 100 µH (744043101) en un sistema sin compensación de reloj.

| L (µH) y número de pieza | C (µF) | SPI SCLK máximo (MHz) | SCLK SPI máximo fijado por | Min SPI SCLK | Longitud máxima del cable RS-485/RS-422 (m) |

| 100 (744043101) | 3.3 | 5.2 | Retraso de propagación del sistema | 2.6 MHz | 10 |

| 1000 (76877530) | 4.7 | 2.4 | Inductor SRF | 700 kHz | 60 |

| 2200 (7687714222) | 10 | 1.2 | Inductor SRF | 350 kHz | >100 |

Si utilizas inductancias más grandes, como 2200 µH, tendrás que añadir capacitancia y resistencia adicionales en la red para amortiguar las resonancias del sistema. Los componentes adicionales están coloreados en azul y se denominan RAMORTIGUADOR (1 kΩ) y CDAMPÓN (47 µF) en la figura 9.

Figura 9. Añade una amortiguación adicional al sistema para los filtros con mayor inductancia y capacitancia.

Configuración experimental

La figura 10 muestra la plataforma de evaluación CbM cableada de Analog Devices, en adelante denominada Pioneer 1. Este sistema utiliza las soluciones de diseño SPI a RS-485/RS-422 presentadas en la primera parte de este artículo. La Pioneer 1 también incluye el acelerómetro MEMS triaxial ADcmXL3021 de gran ancho de banda y bajo ruido, que combina un alto rendimiento con una gran variedad de procesamientos de señales para simplificar el desarrollo de nodos de sensores inteligentes en sistemas CbM. El esclavo SPI a RS-485/RS-422 extiende la salida SPI del ADcmXL3021 a más de 10 m hasta el controlador maestro para el análisis de los datos de vibración. Los diseños de SPI a RS-485 utilizan inductores de 100 µH y condensadores de 3,3 µF para minimizar el tamaño de las soluciones de interfaz esclava, que miden 26 mm × 28 mm (sin contar el conector de interfaz).

Figura 10. Sistema de evaluación de la monitorización del estado por cable Pioneer 1.

Formas de onda de datos de CA en los cables de alimentación fantasma

La Figura 11 y la Tabla 4 describen las tensiones medidas en el maestro y el esclavo SPI, y en el bus de tensión diferencial RS-485/RS-422. Estas tensiones se midieron utilizando la configuración de la aplicación de ejemplo de la Figura 10. Las señales analógicas 1 (amarilla) y 2 (azul) son la representación de la tensión diferencial del bus de la señal MISO (púrpura), medida en la salida del esclavo SPI. La señal digital 4 (amarilla) representa la MISO muestreada en el controlador maestro. La señal MISO en el maestro SPI se corresponde con la polaridad y la fase de la MISO en el esclavo SPI, con un pequeño retraso de propagación.

Figura 11. Tensiones medidas en el maestro y el esclavo SPI, y en el bus de tensión diferencial RS-422.

| Parámetro | Implicaciones para el tamaño de los paquetes |

| 2 Digital (rojo) | ADcmXL3021 BUSY medido en el maestro |

| 3 Digital (naranja) | ADcmXL3021 MOSI medido en el maestro |

| 4 Digital (amarillo) | ADcmXL3021 MISO medido en el maestro |

| 5 Digital (verde) | ADcmXL3021 SCLK medido en el maestro |

| 6 Digital (azul) | ADcmXL3021 CS medido como maestro |

| 3 Analógico (púrpura) | ADcmXL3021 MISO medido en el esclavo |

| 2 Analógico (azul) | Estado de la tensión del bus del pin Z de RS-422 correspondiente a MISO; el diferencial Y a Z corresponde a 3 Analógico (morado) y 4 Digital (amarillo) |

| 1 Analógico (amarillo) | Estado de la tensión del bus del pin Y del RS-422 correspondiente a MISO; el diferencial Y a Z corresponde a 3 Analógico (morado) y 4 Digital (amarillo) |

Corrección de CC en los cables de alimentación fantasma

La figura 12 ilustra los modos normales del ADcmXL3021, que incluyen un protocolo SPI que envía ráfagas de datos de 16 bits a través de MISO, seguidas de un periodo de espera (16 µs mín.), y luego otra ráfaga de datos de 16 bits.

Figura 12. Corrección de CC en los cables de alimentación fantasma.

En una red de potencia fantasma, donde se utilizan inductores de 100 µH y condensadores de 3,3 µF:

- Al final de la trama (EOF), la tensión del bus RS-485/RS-422 vuelve a un estado estable de CC.

- El estado estable de CC del periodo de bloqueo será una tensión diferencial RS-422 B-A > 500 mV, que refleja el estado MISO highZ del ADcmXL3021 y también proporciona un 0 lógico a la salida del transceptor ADM4168E. Esta precisión del estado de reposo está garantizada si se utilizan las resistencias de 500 Ω, como se muestra en el circuito del filtro de la figura 4.

- El siguiente inicio de trama (SOF) cambiará entonces correctamente de bajo a alto, o permanecerá bajo dependiendo de la salida de datos MISO del ADcmXL3021.

- El periodo de caída del estado estacionario del bus RS-485/RS-422 no está alineado con el flanco SCLK del SPI, por lo que el ruido aleatorio no afectará al muestreo de datos MISO del SPI durante este periodo.

En una red de potencia fantasma, donde se utilizan inductores de 1000 µH y condensadores de 4,7 µF

- El EOF, el periodo de abandono y el SOF siguen la salida MISO del ADcmXL3021, y los niveles de tensión del bus no vuelven a caer al estado estable mínimo de CC de 500 mV durante el periodo de abandono. Puede producirse un cierto decaimiento de los niveles de tensión, pero no hasta los niveles de 500 mV.

Solución de evaluación por cable

Analog Devices ha desarrollado la solución de evaluación del sistema por cable Pioneer 1 para soportar el acelerómetro triaxial MEMS ADcmXL3021. Los kits de evaluación Pioneer 1, descritos en esta guía wiki, también pueden admitir los dispositivos MEMS enumerados en la Tabla 5 utilizando la placa de expansión descrita en la guía wiki.

| Parte | Densidad de ruido (µg/√)Hz) | Rango (g) | BW (Hz) | # Ejes |

| ADcmXL3021 | 26 | 50 | 10000 | 3 |

| ADXL357 | 80 | 10, 20, 40 | 1000 | 3 |

| ADXL372 | 200 | 3200 | 3 | |

| ADXL355 | 20 | 2, 4, 8 | 1000 | 3 |

| ADXL313 | 250 | 0.5, 1, 2, 4 | 1600 | 3 |

| ADXL363 | 550 | 2, 4, 8 | 200 | 3 |

| ADXL375 | 200 | 1600 | 3 | |

| ADXL362 | 175 | 2, 4, 8 | 200 | 3 |

| ADXL345 | 420 | 2, 4, 8, 16 | 1600 | 3 |

| ADXL350 | 1, 2, 4, 8 | 1600 | 3 | |

| ADXL343 | No | 2, 4, 8, 16 | 1600 | 3 |

| ADXL312 | 340 | 1.5, 3, 6, 12 | 1600 | 3 |

Referencias

1 Richard Anslow y Dara O'Sullivan. "Habilitación de una sólida monitorización por cable basada en el estado para la Industria 4.0-Parte 1" Analog Devices, Inc. en julio de 2019.

2 "IEEE 802.3bu-2016 - Norma Ethernet del IEEE - Enmienda 8: Capa física y parámetros de gestión para la alimentación por línea de datos (PoDL) de Ethernet de par trenzado simple." IEEE, febrero de 2017.

3 Andy Gardner. "PdL: Presentación de la red de desacoplamiento." Tecnología lineal, mayo de 2014.

4 Andy Gardner. "Cortocircuito momentáneo del conector PoDL y del cable." Tecnología lineal, septiembre de 2014.

Si quieres conocer otros artículos parecidos a Permitir una sólida monitorización por cable basada en el estado para la Industria 4.0-Parte 2 puedes visitar la categoría Generalidades.

Deja una respuesta

¡Más Contenido!