Sustitución de osciladores sintonizados con YIG por silicio mediante un PLL/VCO de banda ultraancha con control de fase de precisión

Los instrumentos de radiofrecuencia y microondas, como los analizadores de señales y redes, necesitan señales de banda ancha y de barrido de frecuencia para realizar muchas de sus mediciones básicas. Sin embargo, perversamente, los osciladores controlados por tensión (VCO) de banda ancha suelen tener el peor ruido de fase debido a su bajo Q y su elevado KVCOS (la sensibilidad de sintonía de un VCO en MHz/V) necesarios para maximizar sus rangos de sintonía. Los osciladores sintonizados de granate de itrio (YIG) resuelven perfectamente este problema con un buen rendimiento de ruido de fase de banda ancha y un rango de sintonización de frecuencia de una octava, pero pueden ser grandes, caros y consumir cientos de mA de corriente debido a sus corrientes de sintonización. Y, por supuesto, siguen necesitando un bucle de bloqueo de fase (PLL) externo para cerrar el bucle y una fuente de corriente controlada por tensión para proporcionar su corriente de sintonización.

Una esfera de cristal YIG se asemeja a un circuito LC de alta calidad cuya frecuencia de resonancia es linealmente proporcional a un campo magnético aplicado externamente. El oscilador se sintoniza mediante una corriente a través de un bucle de una vuelta en una octava o más en el rango de GHz. Los osciladores sintonizados con YIG tienen una baja fluctuación de fase, y sus características de banda ancha de unos 2 GHz a 18 GHz (con una curva de sintonización muy lineal) los convierten en una opción popular para muchas aplicaciones de medición.

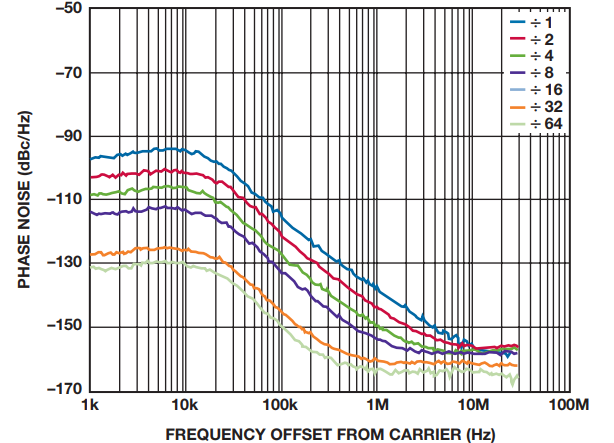

Sin embargo, la diferencia de rendimiento entre los osciladores sintonizados con YIG y los circuitos integrados PLL/VCO se está reduciendo. Por ejemplo, los recientes avances en los circuitos integrados PLL/VCO, como el ADF4355 de Analog Devices, han mejorado significativamente el ruido de fase en comparación con sus predecesores. También han resuelto el problema del amplio rango de sintonización mediante técnicas de diseño como la división del rango de frecuencias de salida en varias subbandas adyacentes, en las que cada subbanda puede tener un VCO de conmutación de banda dedicado para aumentar el rango de sintonización, al tiempo que los VCO de conmutación de banda parecen un único VCO con un KVCO (mostrado en la Figura 1) al usuario. A continuación, los divisores y duplicadores de frecuencia auxiliares amplían la cobertura de frecuencia del rango de sintonización del VCO tanto por arriba mediante la multiplicación como por abajo mediante la división. Por ejemplo, el rango de sintonía fundamental del ADF4355 de 3,4 GHz a 7,2 GHz se amplía hasta 54 MHz por división. Cada vez que se reduce la frecuencia a la mitad, el ruido de fase mejora en 3 dB (véase la figura 2).

Figura 1. El VCO multibanda PLL/VCO del ADF4355 consiste en un conjunto de osciladores, cada uno de los cuales sintoniza una fracción de toda la banda y mantiene un KVCO y, por tanto, VTUNE en toda la gama. La forma del trazado de la tensión de sintonía se asemeja a un diente de sierra porque cada oscilador tiene condensadores fijos que se conmutan en paralelo con la capacitancia de la tensión variable, uno por uno, para maximizar el rango de sintonía global de cada VCO.

Figura 2: Cada vez que la frecuencia de salida se reduce a la mitad, el ruido de fase global mejora en 3 dB. En este caso, dividiendo el VCO de 3,4 GHz por 64 GHz se obtiene un ruido de fase mejor que -130 dBc/Hz para un desplazamiento de 10 kHz a 53,125 MHz.

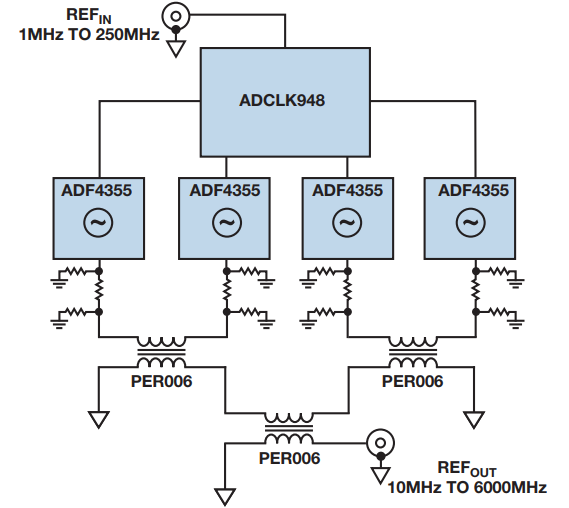

Sin embargo, aunque un CI PLL/VCO tiene un rango de sintonización más comparable al de un oscilador sintonizado con YIG, sigue habiendo un problema: los osciladores sintonizados con YIG siguen ofreciendo un rendimiento de ruido de fase 12 dB mejor que los mejores VCO integrados. Incluso esta brecha puede reducirse, si no se ha cerrado ya, combinando las salidas de varios PLL/VCO en paralelo (como se muestra en la figura 3). Se pueden sumar las salidas y mejorar el ruido de fase en 3 dB por cada duplicación (3 dB) del número de PLL/VCO en paralelo. Por ejemplo, dos PLL/VCO ADF4355 proporcionan una mejora de 3 dB, cuatro PLL/VCO ADF4355 proporcionan una mejora de 6 dB y ocho PLL/VCO ADF4355 proporcionan una mejora de 9 dB (como se muestra en la Figura 4).

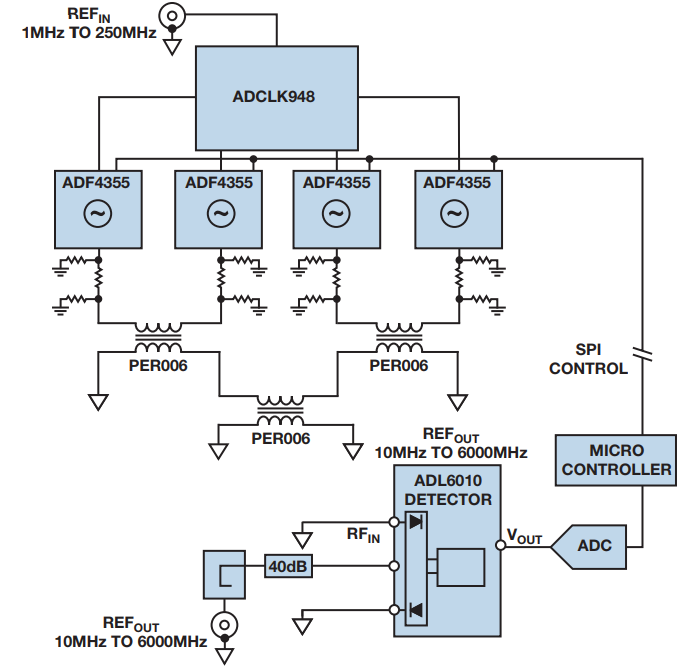

Figura 3: Al sincronizar varios PLL/VCO y combinar sus salidas, puedes mejorar el ruido de fase en 3 dB por cada duplicación del número de VCO. Aquí se muestran cuatro ADF4355 en paralelo y proporcionan una mejora de 6 dB en el ruido de fase global.

Figura 4: Al bloquear la fase y combinar las salidas de ocho PLL/VCO del ADF4355, puedes mejorar el ruido de fase global en casi 9 dB respecto al de un solo PLL/VCO. El espectro muestra tanto el ruido de fase de la salida de un solo ADF4355 como el ruido de fase de la suma de las salidas de ocho ADF4355 sincronizados que funcionan en paralelo.

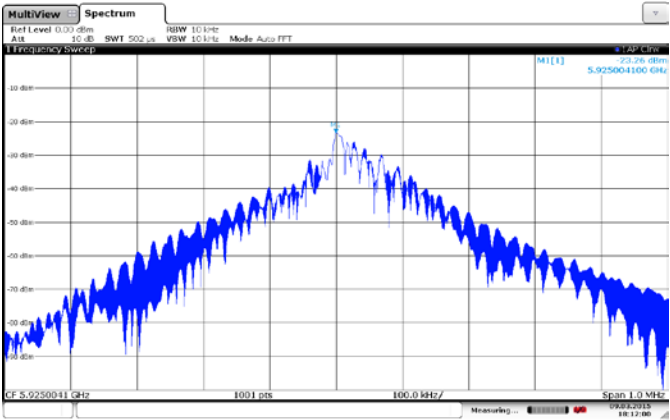

La clave para sumar las salidas de los PLL/VCO es hacer funcionar las salidas de todos los osciladores en fase. El ejemplo que comentaremos aquí utiliza cuatro PLL/VCO en paralelo. Como es de suponer, colocar cuatro bucles de bloqueo de fase y osciladores controlados por tensión a la misma frecuencia en la misma placa de circuito presenta una serie de retos. El principal de estos retos es el aislamiento. Un mal aislamiento entre los bucles de bloqueo de fase puede provocar un fenómeno conocido como bloqueo por inyección (como se muestra en la figura 5), en el que un oscilador se bloquea con una señal fuerte o con uno de sus armónicos, preferentemente a la frecuencia seleccionada por la tensión de sintonización proporcionada por el propio bucle de bloqueo de fase. El bloqueo por inyección es observable al ver una degradación inicialmente sutil del ruido y del desorden, ya que ambos mecanismos de bloqueo generan una distorsión de intermodulación. En los peores casos, la señal se parecerá más a una portadora modulada que a un tono sinusoidal continuo.

Figura 5. El bloqueo por inyección se produce cuando la frecuencia de un VCO se bloquea con una oscilación externa en lugar de con su tensión de control. El resultado es un aumento del ruido de intermodulación y de fase.

El aislamiento requiere una serie de técnicas y circuitos. Por ejemplo, la señal de referencia de cada PLL (REFINA y REFINB) utilizando un buffer, en este caso el buffer de reloj ADI ADCLK948 LVPECL 8:1. Además, para minimizar la diafonía, es necesario que las terminaciones de las patillas de la fuente y de la carga sean correctas, lo más cerca posible de la fuente y de la carga. También se ha incluido un condensador adicional de derivación a tierra (18 pF) para mitigar cualquier fuga de la salida del VCO mientras se pasa la frecuencia de referencia deseada.

Otras vías que requieren aislamiento son las líneas de alimentación. Para proporcionar el aislamiento necesario, cada PLL tiene su propio regulador de alto rendimiento (el ADI ADM7150), uno para los +5 V, VVCOvP, y VREGVCOlas fuentes de alimentación del VCO son las más críticas aquí. La fuente de alimentación analógica (AVDD), digital (DVDD), y la etapa de salida (VRF) también requieren 3,3 V, y también se utilizan reguladores independientes para cada línea. Es aceptable conectar las líneas de 3,3 V de cada PLL juntas, siempre que se haya utilizado un buen desacoplamiento.

En la etapa de salida de RF, la salida auxiliar (RFOUTB+]) y REFOUTB-) se desactiva y termina para garantizar que no se generen tonos no deseados. Salida de RFOUTA- está terminada en una carga de 50 Ω, y su salida complementaria, RFOUTA+se envía a un combinador de potencia de alto aislamiento (Marki Microwave, PBR0006SMG). Este combinador se eligió para garantizar que el acoplamiento entre las etapas de salida se mantuviera al mínimo, a la vez que proporcionaba una señal combinada en la salida común. Para mejorar el aislamiento, un par de ellos combinan las salidas de dos PLL, y un tercer combinador suma las salidas de los dos primeros.

Por último, un escudo Laird estándar proporciona un aislamiento adicional para minimizar cualquier radiación parásita que pueda acoplar electromagnéticamente los VCO. En conjunto, todos estos pasos garantizan el mejor aislamiento posible.

El ADF4355 contiene un modulador de alta resolución de 24 bits que, además de permitir la generación de valores de división N fraccional, también contiene circuitos que permiten realizar pequeños ajustes en la fase de la señal de RF. Para que sean útiles, los valores de fase deben ser repetibles. Para ello es necesario utilizar la función de resincronización de fase.

La resincronización de fase se describe mejor como una función que pone el divisor fraccionario (un modulador ∑-∆ con conformación de ruido) en un estado conocido tras una actualización de la frecuencia. Como la fase es una medida relativa, la función de resincronización se define como funcional al pasar de una frecuencia F1 con una fase P1 a una frecuencia F2, y al volver a la frecuencia F1, la fase debe ser de nuevo P1 como en la primera medición. Esta función, combinada con la resincronización, nos permite ajustar la fase para minimizar la diferencia de fase entre cada uno de los cuatro PLL para obtener la máxima suma de la potencia de los cuatro PLL y, por tanto, la mayor mejora del ruido de fase. Además de estos pasos, también es importante restablecer los contadores de cada PLL simultáneamente, lo que se consigue fácilmente mediante un apagado y encendido por hardware utilizando el pin de habilitación del chip (CE).

La variación del proceso y de las piezas significa que no podemos suponer que la diferencia de fase entre cada PLL, tras los procedimientos de reajuste y resincronización, será lo suficientemente cercana a cero como para maximizar la relación señal/ruido, por lo que es necesario un circuito de calibración externo.

El procedimiento de calibración es sencillo: enciende un solo PLL/VCO y pon su fase a cero. Enciende sucesivamente cada PLL/VCO adicional, cambia su fase de salida hasta que la potencia de salida combinada de los PLL/VCO encendidos sea máxima, entonces enciende el siguiente VCO y vuelve a ajustar su fase hasta que la potencia de salida combinada de los PLL/VCO sea de nuevo máxima. Nota: El mayor cambio de potencia se produce cuando se enciende el segundo PLL/VCO, ya que la potencia combinada se duplica; la diferencia disminuye para cada PLL/VCO posterior. En la práctica, esto significa que la relación señal/ruido aumenta cada vez que se duplica el número de PLL/VCO en paralelo. Es decir, dos en paralelo ofrecen una mejora de 3 dB, cuatro ofrecen una mejora de 6 dB y ocho ofrecen una mejora de 9 dB. Por supuesto, la complejidad del combinador de potencia también se duplica, por lo que cuatro PLL/VCO son un límite superior práctico con rendimientos decrecientes para ocho y 16 PLL/VCO en paralelo.

Ten en cuenta que el mejor rendimiento de fase y la máxima potencia de salida coinciden, por lo que una medición de potencia es suficiente para garantizar el mejor rendimiento de ruido de fase. En nuestro caso, el calibrador es un detector de potencia ADI ADL6010 que mide la amplitud de salida de las señales combinadas. De este modo, se puede ajustar la fase de cada PLL (en cada frecuencia), y el ajuste de fase es constante cuando la potencia combinada ha alcanzado un máximo (como se muestra en la figura 6). Este proceso se repite para cada PLL adicional hasta que los cuatro PLL se hayan encendido y ajustado, de modo que la señal a la salida de los combinadores esté al máximo.

Figura 6. Se muestran cuatro PLL/VCO integrados ADF4355 alineados en fase con un búfer de reloj ADCLK948, combinadores (PBR-0006SMG) y circuitos de calibración.

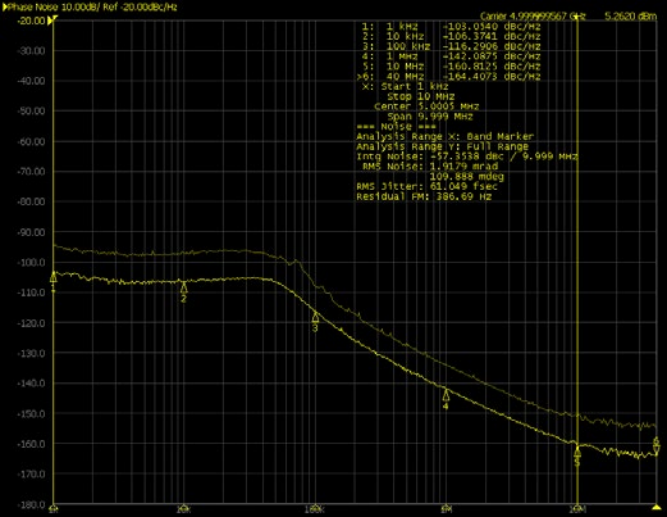

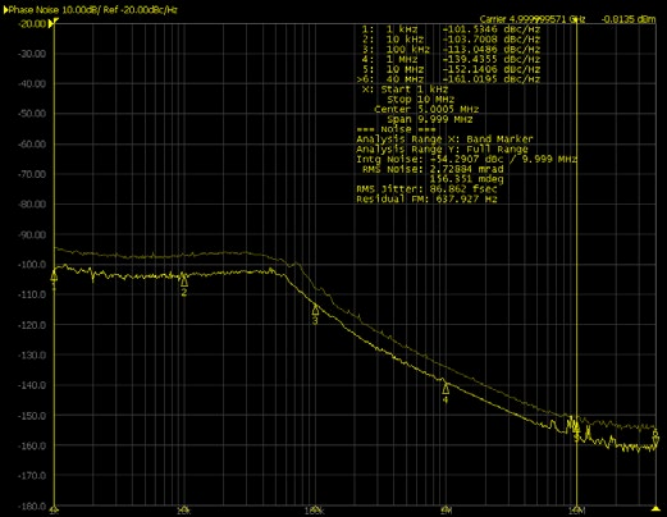

La figura 7 muestra que los resultados prácticos siguen la teoría, que para cada duplicación de PLL/VCO y con la palabra de fase correcta escrita, el ruido de fase combinado de los cuatro PLL/VCO mejora en 6 dB respecto al de un solo PLL/VCO. Así, el rendimiento de un PLL ADF4355 (-134 dBc/Hz con un desfase de 1 MHz) puede mejorarse en 6 dB hasta unos -140 dBc/Hz cuando se combinan cuatro PLL/VCO en fase.

Figura 7. Gráfico de ruido de fase de salida que muestra el ruido de fase de un solo oscilador PLL/VCO ADF4355 y de cuatro ADF4355 combinados en fase.

Si quieres conocer otros artículos parecidos a Sustitución de osciladores sintonizados con YIG por silicio mediante un PLL/VCO de banda ultraancha con control de fase de precisión puedes visitar la categoría Generalidades.

Deja una respuesta

¡Más Contenido!