Mejora de la densidad de la cadena de señales de adquisición de datos de precisión con la tecnología SiP

Un deseo común en el espacio de mercado de la adquisición de datos de precisión es mejorar la densidad de la cadena de señales manteniendo el rendimiento. Como cada vez más aplicaciones adoptan un enfoque de ADC por canal, o intentan meter más canales en el mismo factor de forma, la densidad de canales es una preocupación importante para muchos diseñadores de cadenas de señales de adquisición de datos. Además, hay una tendencia a hacer que los circuitos de precisión sean más fáciles de usar y que alcancen el rendimiento de la hoja de datos con mayor facilidad. Esto ofrece la oportunidad de construir subsistemas que resuelvan estos problemas mediante la implementación de cadenas de señales con tecnología de sistema en paquete (SiP).

La primera familia de dispositivos producida por Analog Devices que utiliza esta estrategia de subsistema es la nueva línea de productos de adquisición de datos ADAQ798x. El ADAQ798x es un subsistema convertidor analógico-digital de 16 bits que integra cuatro bloques comunes de procesamiento y acondicionamiento de señales en un diseño SiP que admite una gran variedad de aplicaciones. El dispositivo también contiene los componentes pasivos más críticos, eliminando muchos de los retos de diseño asociados a las cadenas de señales tradicionales que utilizan convertidores analógico-digitales (ADC) de registro de aproximación sucesiva. Estos componentes pasivos son esenciales para conseguir el rendimiento especificado del dispositivo

Al revisar las aplicaciones y los mercados que utilizan los ADC de SAR, como la industria, la instrumentación, las comunicaciones y la sanidad, se ha comprobado que algunas secciones de las cadenas de señales de adquisición de datos son muy comunes a todas estas aplicaciones, mientras que algunas partes de las cadenas de señales pueden diferir significativamente. Se ha visto que estas cadenas de señales utilizan una gama variada de fuentes de entrada y sensores. Por lo tanto, se aplicarán varias formas de acondicionamiento de la señal antes de presentarla al ADC. Como las fuentes varían, esto significa que las escalas completas del sistema pueden ser diferentes y requieren valores de referencia distintos para maximizar el rango dinámico. Algunas aplicaciones son multicanal y, por tanto, implementan un multiplexor frontal. Se aplicarían diferentes esquemas de alimentación en función de los criterios clave de rendimiento de la aplicación. Sin embargo, independientemente de la aplicación, hay componentes que son comunes a muchas de estas aplicaciones. El ADAQ7980 y el ADAQ7988 forman parte de una solución de componentes totalmente activa de Analog Devices que contiene un ADC SAR de 16 bits de alta precisión y bajo consumo; un controlador de ADC de bajo consumo, gran ancho de banda y alta impedancia de entrada; un búfer de referencia estable y de bajo consumo; y un bloque de gestión de energía eficiente. Estos componentes de la cadena de señales se han integrado en un subsistema de adquisición de datos utilizando SiP

Alojado en un pequeño paquete LGA de 5 mm × 4 mm, este novedoso componente simplificará el proceso de diseño de los sistemas de adquisición de datos. El nivel de integración del sistema del ADAQ798x resuelve muchos problemas de diseño, pero el dispositivo sigue ofreciendo la flexibilidad de un bloque controlador de ADC configurable para permitir ajustes de ganancia y/o modo común. Un conjunto de cuatro fuentes de alimentación del dispositivo permite un rendimiento óptimo del sistema, pero el funcionamiento con una sola fuente es posible con un impacto mínimo en las especificaciones de funcionamiento del dispositivo. La familia ADAQ798x ofrece un alto nivel de integración a la vez que es lo suficientemente flexible como para adaptarse a una amplia gama de aplicaciones.

Durante el desarrollo de este producto, ADI analizó los errores de diseño más comunes para determinar cómo ayudar a resolver estos problemas. Se descubrió que muchos de estos errores de diseño en la cadena de señales se centraban principalmente en dos zonas del ADC SAR: la entrada de referencia y la entrada analógica. Muchos de estos errores de la cadena de señales están asociados a los circuitos periféricos del ADC que son fundamentales para el rendimiento general de la conversión analógico-digital. Con respecto a la referencia, los errores más comunes son la disposición y el dimensionamiento incorrectos del condensador de derivación de referencia, la insuficiente potencia de accionamiento de la fuente de referencia y la excesiva densidad espectral de ruido generada por la fuente de referencia. Estas condiciones de diseño inadecuadas para la entrada de referencia de un ADC SAR pueden hacer que el ADC tome decisiones de bits incorrectas. Al igual que con la entrada analógica del ADC, los problemas de diseño más comunes que se han observado son la selección incorrecta del controlador del ADC, el ancho de banda del filtro incorrecto entre el controlador del ADC y el ADC, y la selección incorrecta del material dieléctrico del condensador del filtro. Cualquier combinación de estos problemas de diseño a nivel de sistema puede provocar una grave degradación del rendimiento de conversión del ADC. Las decisiones tomadas en el desarrollo de los dispositivos ADAQ798x tenían como objetivo resolver estos problemas.

Como ya se ha dicho, para conseguir el rendimiento de la hoja de datos de un sistema de conversión basado en el SAR ADC, hay que tener en cuenta ciertas consideraciones de diseño. Las características de la fuente de referencia del ADC SAR y de la fuente de entrada analógica son fundamentales para el éxito del diseño de la cadena de señales de conversión. En general, un ADC SAR requiere una fuente de referencia de baja impedancia y un condensador de desacoplamiento grande y bien colocado. Este condensador de desacoplamiento se utiliza para reponer la carga consumida por el ADC durante la prueba de bits SAR y puede considerarse un componente de la red SAR externo al ADC. El ADC también necesita una fuente de entrada analógica con un rendimiento de ruido y un ancho de banda suficientes para ajustar correctamente la entrada del ADC a la resolución deseada. La figura 1 muestra el diagrama de bloques de los dispositivos ADAQ798x.

Como puede verse en la Figura 1, el ADAQ798x alberga un búfer de referencia y el correspondiente condensador de desacoplamiento de 10 μF. Lo ideal es colocar el condensador de desacoplamiento cerca de la entrada de referencia del ADC. El objetivo de esta colocación de componentes es reducir las impedancias parásitas entre el condensador de desacoplamiento y la red de condensadores SAR. Este camino debe tener una impedancia lo más baja posible para permitir que el condensador añada rápidamente carga al conjunto SAR para su redistribución en el proceso de conversión. Del mismo modo, se controló la resistencia de la traza entre el buffer de referencia y el condensador de desacoplamiento. Se eligió un tamaño de traza que proporcionara una resistencia que mantuviera estable la memoria intermedia de referencia, sin provocar una caída de tensión lo suficientemente grande como para crear un error de ganancia de conversión. El amplificador utilizado para amortiguar la señal de referencia está configurado en ganancia unitaria. Esto presenta una entrada de alta impedancia a la fuente de referencia externa en lugar de presentar la tradicional carga de condensadores conmutados de la entrada de referencia del ADC SAR. El usuario del ADAQ798x puede ahora implementar una referencia de bajo consumo o sin búfer para manejar el pin de entrada de referencia del ADAQ798x (REFIN). Al presentar una alta impedancia, esto también da al usuario más flexibilidad para elegir la ubicación física de la fuente de referencia en la placa de circuito impreso. Al utilizar este componente SiP, la colocación de la fuente de referencia se ha vuelto mucho menos crítica debido a la inclusión de un búfer de referencia bien controlado en el ADAQ798x. Al incluir sólo un búfer y no la fuente de referencia propiamente dicha, el usuario tiene la libertad de elegir una amplia gama de valores de referencia y, en última instancia, maximizar el rango dinámico del sistema con esta selección de referencia, ya que la referencia define la tensión de escala completa del convertidor.

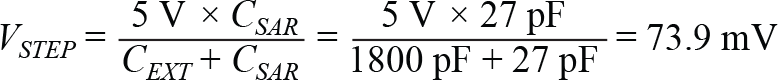

El ADAQ798x también tiene un controlador de ADC y un filtro de paso bajo correspondiente entre el controlador y la entrada del ADC. La selección del ancho de banda del filtro es fundamental para conseguir los niveles de rendimiento deseados. El ancho de banda se selecciona como un compromiso entre el tiempo de asentamiento y el filtrado del ruido de banda ancha del controlador ADC de alta velocidad. Cualquier perturbación en el nodo de entrada del CAD debe resolverse con suficiente resolución durante el tiempo de adquisición del CAD. Cuando un ADC SAR realiza su proceso de conversión, la entrada del ADC se desconecta de sus fuentes de entrada externas. Durante la conversión, el potencial de tensión en la entrada del ADC puede cambiar. Sin embargo, al final de la conversión, la tensión en la red de condensadores SAR es esencialmente la misma que al principio de la conversión. Cuando el ADC vuelve al modo de adquisición (seguimiento), la carga del conjunto de condensadores SAR está ahora presente en la entrada del ADC. Este condensador se coloca en paralelo con el condensador del filtro pasabajos externo. Con tensiones diferentes en estos condensadores, se producirá una redistribución de la carga para equilibrar la tensión en todos estos condensadores. Esto dará lugar a un salto de tensión en la entrada del ADC que deberá ajustarse durante el periodo de adquisición. El peor de los casos se produce cuando se presenta una transición de escala completa al ADC. Este escenario puede darse en sistemas con una entrada multiplexada. Este salto de tensión se mitiga por la relación entre el condensador externo y la capacitancia interna del SAR. Los productos ADAQ798x incluyen un condensador de filtro de paso bajo de 1800 pF. Suponiendo una tensión de referencia de 5 V, el paso máximo de tensión de entrada del ADC se calcula como sigue:

Este paso de tensión debe ajustarse dentro del tiempo mínimo de adquisición de 290 ns. El número de constantes de tiempo necesarias para establecer este paso de tensión puede calcularse como el logaritmo natural de la relación entre el tamaño del paso y el error de asentamiento. El error de liquidación se elige como ½ LSB. Por lo tanto, el número de constantes de tiempo se encuentra por :

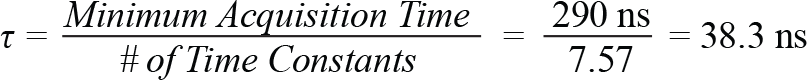

Una vez conocido el número de constantes de tiempo, se puede determinar la tau (τ) del filtro RC de paso bajo:

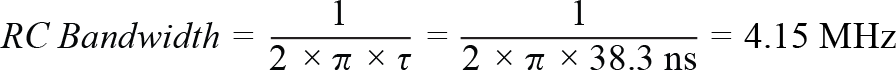

Esta tau puede utilizarse para determinar el ancho de banda del filtro necesario con la siguiente ecuación:

Para proporcionar cierto margen y utilizar componentes de valor estándar, los productos ADAQ798x incluyen un filtro formado por una resistencia de 20 Ω y un condensador de 1800 pF. Esto da un ancho de banda del filtro de 4,42 MHz, lo que permite al filtro del ADAQ798x sintonizar los mayores pasos de tensión previstos en el tiempo de adquisición del ADC. El ancho de banda del filtro calculado también representa el punto de compromiso entre el filtrado del ruido y la liquidación. Si utilizas un ancho de banda de filtro cercano al mínimo necesario para garantizar el asentamiento, maximizarás el beneficio de filtrado de ruido del filtro pasivo de paso bajo.

Aunque el paso de tensión del ADC SAR que vuelve al modo de adquisición es el factor limitante para calcular el ajuste del filtro, hay que tener en cuenta que el filtro también puede ajustar la variación de tensión real de un paso de escala completa del multiplexor bien dentro del periodo mínimo de conversión de 1 μs. Para establecer un paso a escala completa con una resolución de ½ LSB, se necesitan 11,78 constantes de tiempo. Esta cifra se calcula a partir del logaritmo natural del número N+1 de niveles de cuantificación. En este caso, 217 o los códigos 131072. 11.78 constantes de tiempo a 38,3 ns por constante de tiempo, es decir, unos 450 ns, lo que no es preocupante comparado con el periodo de conversión de 1 μs. Esto supone que el canal del multiplexor se conmuta directamente después de iniciar una conversión

El ancho de banda del controlador del ADC también es muy importante para garantizar un buen rendimiento de la cadena de señales de conversión. En la ganancia unitaria, el factor limitante de la configuración es el paso de tensión que debe establecerse en 290 ns y que está asociado al retorno del convertidor al modo de adquisición. Por tanto, en este caso, el ancho de banda de la señal pequeña es la especificación más importante del ancho de banda del amplificador. Para establecer un paso de escala completa del multiplexor dentro del periodo mínimo de conversión de 1 μs, hay que mantener un gran ancho de banda de la señal del controlador del ADC que permita 11,78 constantes de tiempo en el periodo de 1 μs.

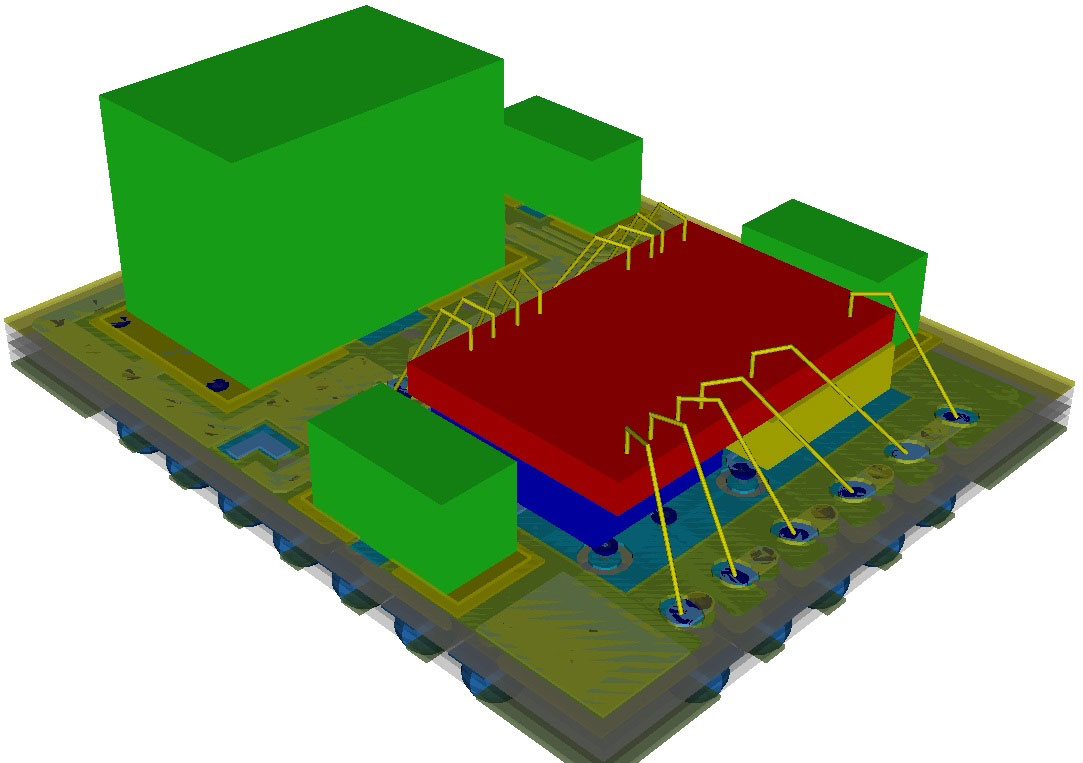

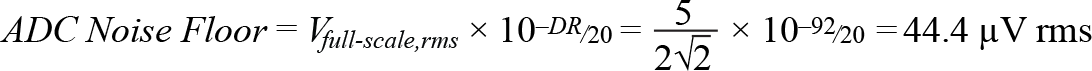

El controlador del ADC no debe aportar un ruido excesivo a la cadena de señales de conversión. El rendimiento de ruido total del subsistema se calcula como la combinación de la raíz cuadrada del ruido del ADC, el ruido del controlador del ADC y el ruido del buffer de referencia. Debido al limitado ancho de banda del circuito de referencia por el gran condensador de derivación, el ruido del buffer de referencia es despreciable en el cálculo del RSS. Se eligió como objetivo que el ruido del controlador del ADC en una configuración de ganancia unitaria no fuera superior a ⅓ del ruido del ADC. El controlador del ADC está especificado para tener una densidad espectral de ruido de 5,2 nV/√Hz. Para calcular el ruido global del sistema, hay que convertir la densidad espectral del ruido del controlador ADC en μV rms con la siguiente ecuación:

El ADC tiene una especificación de rango dinámico típico de 92 dB con una referencia de 5V. El umbral de ruido del ADC puede calcularse como sigue:

Con un suelo de ruido del controlador ADC de 13,7 μV rms, esto queda por debajo del objetivo de ⅓ de ruido del ADC. El rango dinámico global del sistema se reduce de 92 db a 91,6 dB debido a la contribución del ruido del controlador ADC en una configuración de ganancia unitaria. Debido al impacto limitado del controlador del ADC en el ruido del sistema, no es necesario cambiar el ancho de banda del filtro de paso bajo para las aplicaciones de menor frecuencia de muestreo que ofrecen más tiempo de asentamiento debido a períodos de adquisición más largos. La mejor mejora de la ganancia unitaria que puede esperarse reduciendo el ancho de banda del filtro sería recuperar la pérdida de 0,4 dB de rango dinámico. Sin embargo, aumentar la resistencia del filtro para reducir el ancho de banda puede tener efectos adversos en el rendimiento de la THD, mientras que el controlador del ADC puede tener dificultades para manejar cargas capacitivas más grandes. Si se necesita un filtrado adicional, el controlador ADC puede configurarse para proporcionar una ventaja de filtrado.

Los productos ADAQ798x también incluyen un regulador lineal CMOS LDO de bajo ruido de 2,5 V. Algunos productos ADC SAR requieren una fuente de alimentación específica de 2,5 V con un pequeño rango de tolerancia. Para los usuarios que no dispongan de un raíl de alimentación de 2,5 V, hay que generar uno específicamente para el ADC. Con este componente, las fuentes de alimentación se han simplificado mucho al incluir el LDO. El LDO integrado se utiliza para alimentar el convertidor y la entrada del LDO actúa ahora como fuente de alimentación del ADC. Esto permite una gama mucho más amplia de tensiones de alimentación utilizables. También proporciona un grado de simplicidad. La alimentación positiva del amplificador puede utilizarse como entrada al LDO para crear un sistema de alimentación único. Además, se puede elegir la tensión de alimentación para optimizar el rendimiento o el consumo de energía. La unidad tiene capacidad de apagado total. La flexibilidad de las configuraciones de la fuente de alimentación permite al usuario del ADAQ798x hacer los compromisos más adecuados para su aplicación.

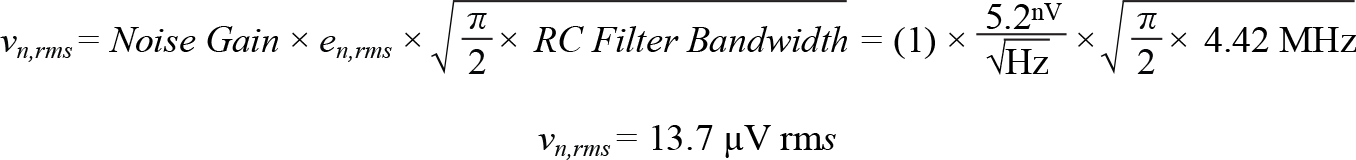

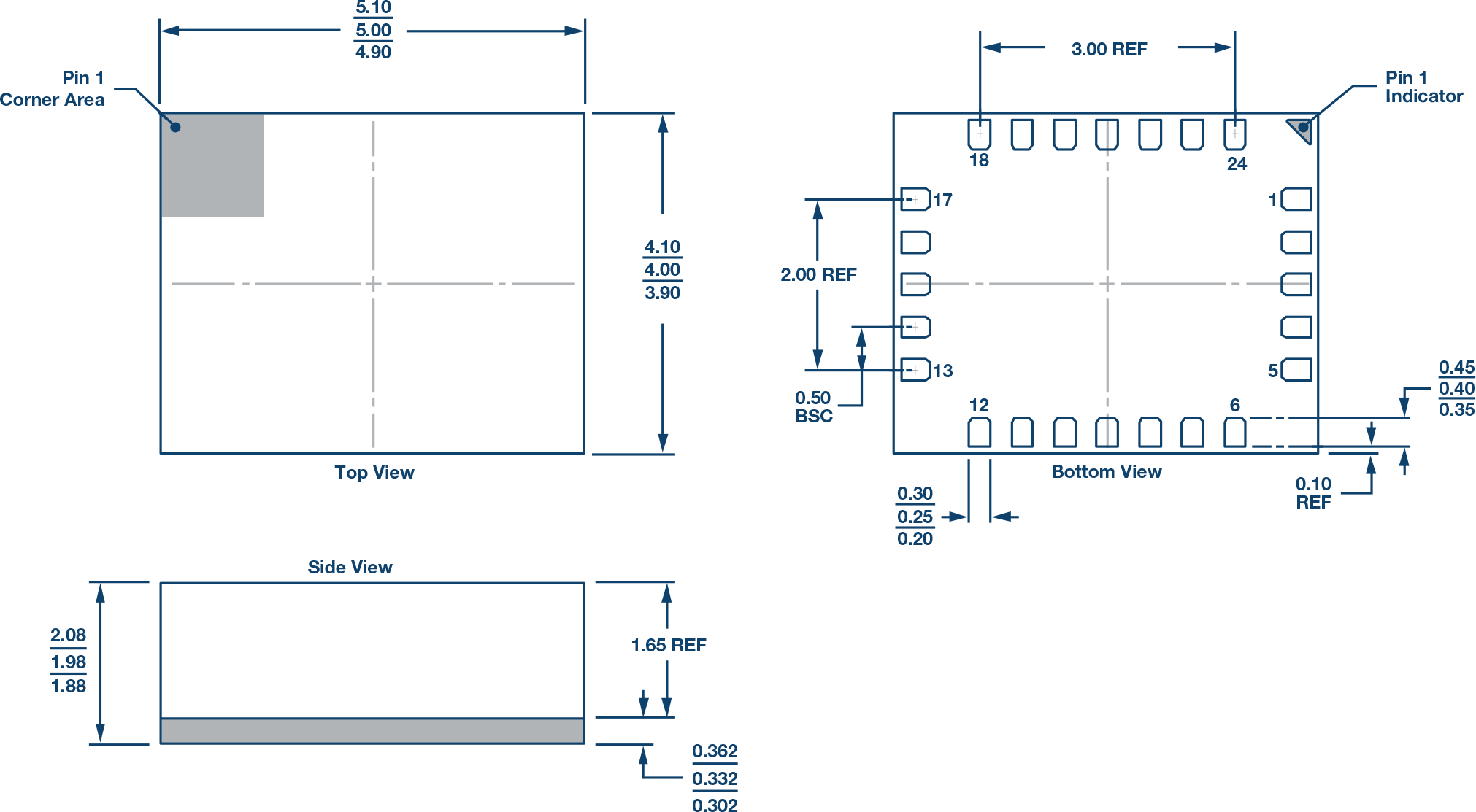

Las dimensiones de la carcasa del ADAQ798x son 5 mm × 4 mm × 2 mm. El laminado de cuatro capas tiene un grosor de 0,35 mm, mientras que la tapa del molde tiene un grosor de 1,65 mm. Este encapsulado de sobremolde tiene un compuesto de molde completo y un relleno inferior, como cualquier CI encapsulado típico. El laminado presenta una huella LGA para el usuario y tiene 24 almohadillas de E/S. La figura 2 muestra el esquema del paquete del ADAQ798x. La figura 3 es un modelo del conjunto ADAQ798x sin ningún tipo de encapsulado o compuesto de moldeo. La figura 3 muestra que el subsistema es una mezcla de componentes activos de Analog Devices y componentes pasivos disponibles en el mercado. Las trazas laminadas se diseñaron para controlar las impedancias y eliminar cualquier efecto de diafonía. La culminación de todas estas técnicas de diseño y montaje ha llevado al desarrollo de un producto que puede ahorrar hasta un 50% de la superficie de la placa de circuito impreso en comparación con diseños similares de componentes individuales.

Además del ahorro de superficie, el ADAQ798x ofrece a los diseñadores de la cadena de señal una mayor posibilidad de conseguir el rendimiento deseado y reduce el riesgo de rediseñar el sistema. En última instancia, esto debería traducirse en un menor tiempo de salida al mercado y menores costes de desarrollo. La nomenclatura del sistema también se ha simplificado al elegir el ADAQ798x, y una mayor parte del sistema está ahora cubierta por una única hoja de datos. Este componente SiP es robusto. Está diseñado y ampliamente cualificado para soportar entornos industriales difíciles. Ofrece excelentes índices de calidad y está especificado en un rango de temperatura de -55°C a +125°C. En general, el ADAQ798x ofrece un equilibrio excepcional entre integración y flexibilidad sin comprometer el rendimiento de la cadena de señal.

Si quieres conocer otros artículos parecidos a Mejora de la densidad de la cadena de señales de adquisición de datos de precisión con la tecnología SiP puedes visitar la categoría Generalidades.

Deja una respuesta

¡Más Contenido!