Introducción a I2C: ¿Qué es I2C? (Parte 1)

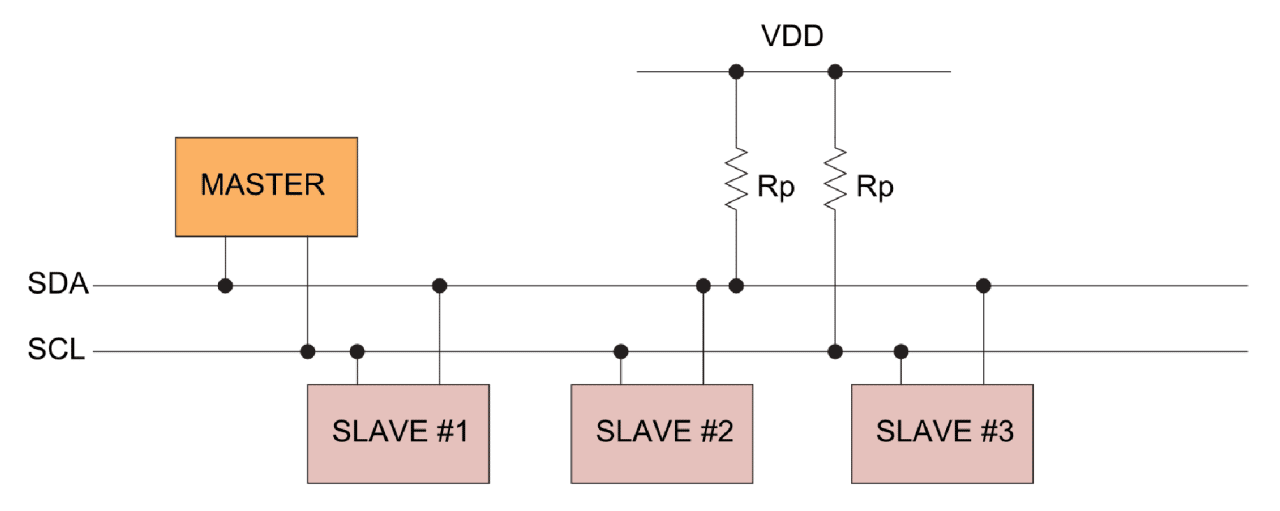

El Circuito Inter-Integrado (I2C) bus es una interfaz serial de dos hilos desarrollada originalmente por Phillips Corporation para su uso en productos de consumo. Es un bus bidireccional que se implementa fácilmente en cualquier proceso de IC (NMOS, CMOS, bipolar) y permite una comunicación simple entre IC. Las conexiones se minimizan mediante el uso de una línea de datos en serie (SDA), una línea de reloj en serie (SCL) y una conexión a tierra común para llevar todas las comunicaciones. yo2C ha ganado una gran aceptación e incluso ha servido como prototipo para System Management Bus (SMBus), que es un subconjunto de I2C.

yo2El protocolo de comunicación C sigue una jerarquía maestro/esclavo, en la que el maestro se define como el dispositivo que cronometra el bus, se dirige a los esclavos y escribe o lee datos hacia y desde los registros en los esclavos. Los esclavos son dispositivos que responden solo cuando son interrogados por el maestro, a través de su dirección única. Por lo tanto, es imperativo evitar la duplicación de direcciones entre los esclavos. Los esclavos nunca inician una transferencia de datos.

el yo2El bus C usa solo dos líneas bidireccionales, línea de datos en serie (SDA) y una línea de reloj en serie (SCL). yo2Los dispositivos compatibles con C se conectan al bus con colector abierto o pines de drenaje abiertos que tiran de la línea a nivel BAJO. Cuando no hay transmisión de datos el I2C las líneas de bus inactivas en estado ALTO; las líneas se tiran pasivamente hacia arriba.

La transmisión ocurre alternando las líneas tirando de BAJO y soltando ALTO. Los bits se cronometran en los flancos descendentes del reloj. La velocidad de transferencia de datos estándar es de 100 kbits/s, mientras que la velocidad de transferencia del modo rápido es de 400 kbits/s.

Figura 1: I generalizado2Diagrama de conexión C

el yo2El bus C puede admitir múltiples dispositivos, tanto ESCLAVO como MAESTRO, y la única limitación es la capacitancia en el bus (400pF) y el espacio de direcciones (128 direcciones únicas) a medida que se agregan más dispositivos.

yo2Los paquetes de datos C se organizan en bytes de 8 bits que comprenden la dirección del esclavo, el número de registro y los datos que se transferirán. La transmisión a través del bus es una operación de lectura o escritura. Los protocolos de lectura y escritura se basan en una serie de subprotocolos, como condiciones de inicio y parada, bits de inicio repetidos, byte de dirección, bits de transferencia de datos y bits de reconocimiento/no reconocimiento.

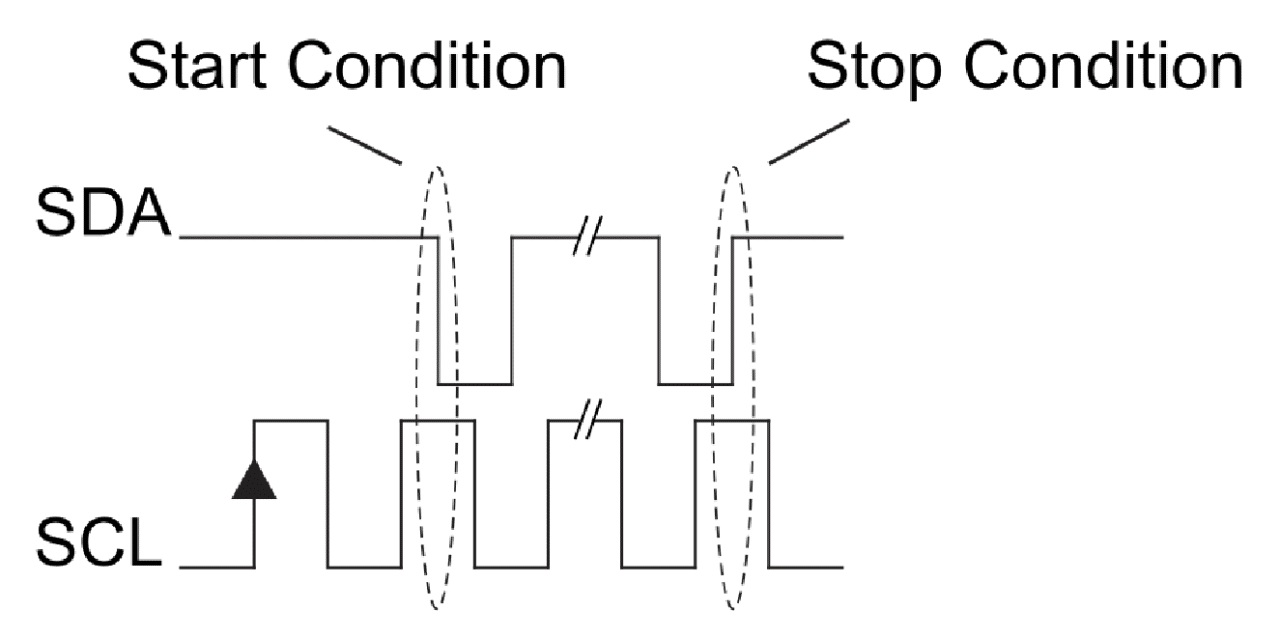

Como sugiere el nombre, una condición de inicio siempre ocurre al comienzo de una transmisión y es iniciada por el dispositivo MAESTRO. Esto se hace para activar los dispositivos SLAVE inactivos en el bus. Esta es una de las dos veces que se permite que la línea SDA cambie de estado cuando SCL es alto. Para indicar una condición de inicio, la línea SDA pasa del estado ALTO al estado BAJO, mientras que SCL está en ALTO.

Figura 2: Transiciones de condición de inicio y condición de parada

Similar a una condición de inicio, la condición de parada ocurre al final de una transferencia de datos y también es generada por el MAESTRO. Esto significa el final de la transferencia y es un comando para decirle a los dispositivos esclavos que deben volver a un estado inactivo, liberar la línea SDA y no enviar más datos en el bus. Esta es la segunda instancia en la que se permite que la línea SDA cambie de estado cuando SCL está en ALTO. La línea SDA pasa del estado BAJO al ALTO, mientras que SCL es ALTO, para indicar una condición de parada.

En todas las demás condiciones, la línea SDA solo cambia de estado cuando la línea SCL está en BAJO.

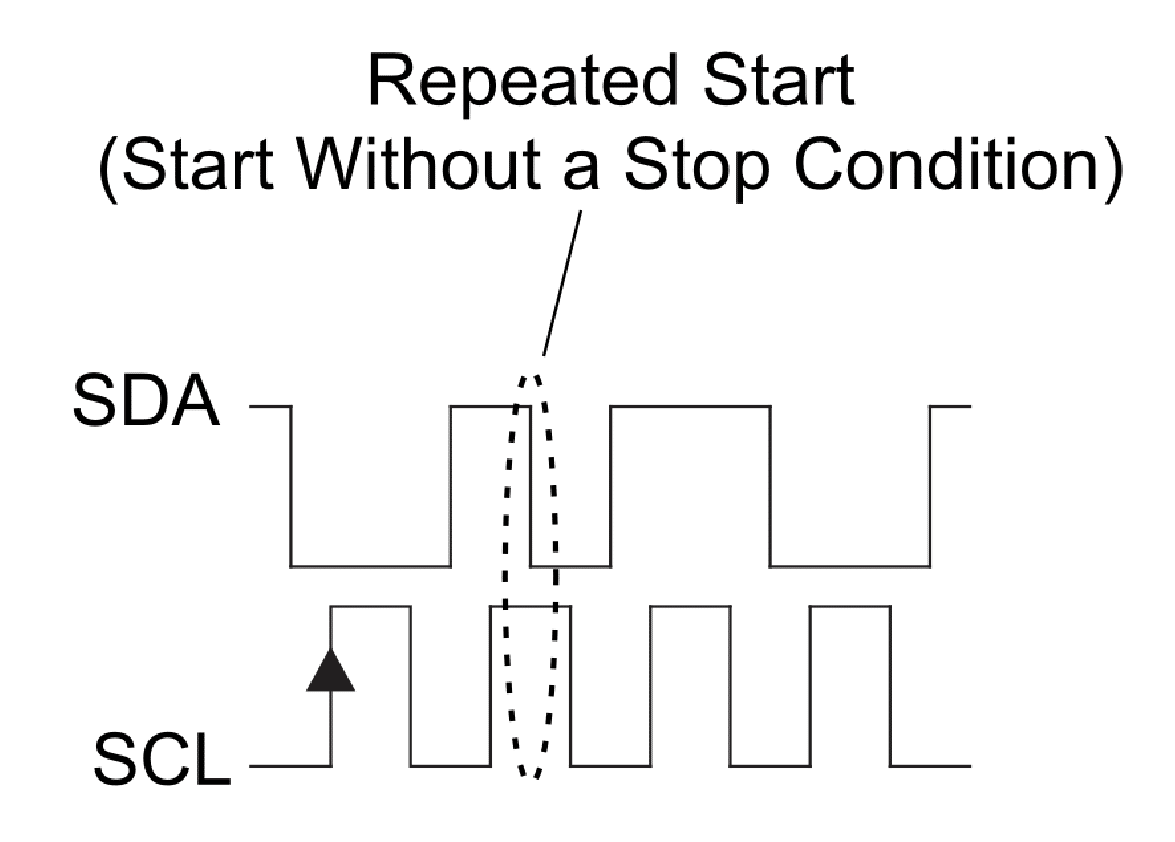

Una condición de inicio puede repetirse durante una transmisión sin necesidad de terminar primero con una condición de Parada. Este es un caso especial, llamado Inicio repetido, y se usa para cambiar la dirección de transmisión de datos, repetir intentos de transmisión, sincronizar varios circuitos integrados o incluso controlar la memoria en serie.

Figura 3: La condición de inicio repetido es esencialmente una condición de inicio en medio de una I2C Transacción sin una condición de parada anterior

Una dirección de esclavo se envía en formato de bytes de 8 bits, MSB primero, pero el último bit indica si la transacción leerá o escribirá en el esclavo. En efecto, los 7 bits superiores constituyen la dirección del esclavo, mientras que el 8º bit sirve como bit de comando READ/WRITE#. Por lo tanto, hay un espacio de direcciones de 128 direcciones únicas para direccionar hasta 128 esclavos. Muchas veces.

Por ejemplo, después de una condición de inicio, el MAESTRO envía un byte de dirección que corresponde a la dirección única de un dispositivo ESCLAVO en el bus. Cada uno de los dispositivos en el bus tiene sus propias direcciones fijas o programadas. Los ESCLAVOS en el I2El bus C responde al comando de inicio escuchando activamente los primeros siete bits del primer byte enviado. Si los primeros siete bits coinciden con la dirección del dispositivo ESCLAVO, continúa leyendo el octavo bit (lectura/escritura#bit) del byte de dirección. Todos los demás dispositivos SLAVE ignoran el resto de la transacción. Un BAJO en el bit READ/WRITE# especifica que el MAESTRO escribirá datos en el dispositivo ESCLAVO direccionado, y para un ALTO, el MAESTRO leerá datos del dispositivo ESCLAVO. Una vez que el ESCLAVO correspondiente haya leído el byte de dirección, reconocerá esta transferencia enviando un bit de reconocimiento tirando de SDA BAJO para el período de pulso ALTO del reloj adyacente y luego asumirá el papel de un esclavo-transmisor o esclavo-receptor dependiendo de la LECTURA /ESCRIBIR# bit enviado.

A partir de este punto, a menos que se envíe un bit de parada, el ESCLAVO asume que, dado que ya se ha direccionado, todas las comunicaciones se dirigen a él.

Como forma de retroalimentación, después de cada transmisión de bytes, el dispositivo receptor envía un bit de reconocimiento o no reconocimiento. El receptor genera un bit de reconocimiento manteniendo la línea SDA baja durante un período ALTO de SCL, mientras que un bit de no reconocimiento se genera cuando el receptor deja la línea SDA pasivamente en ALTO y no responde de ninguna manera. Este hecho implica que en respuesta a un byte de dirección, todos los SLAVE no coincidentes envían un bit de Not Acknowledge al no responder.

Se utiliza un ACK para indicar que un byte (dirección o datos) se transmitió y recibió con éxito y que la transmisión puede continuar hasta la siguiente transferencia de bytes, una condición de parada o un inicio repetido (Figura 4). El receptor generalmente usa un NACK para indicar si ocurrió un error en algún lugar de la transmisión de datos. Esto se utiliza para enviar una señal al dispositivo de transmisión para que finalice la transmisión inmediatamente o para hacer otro intento enviando un inicio repetido.

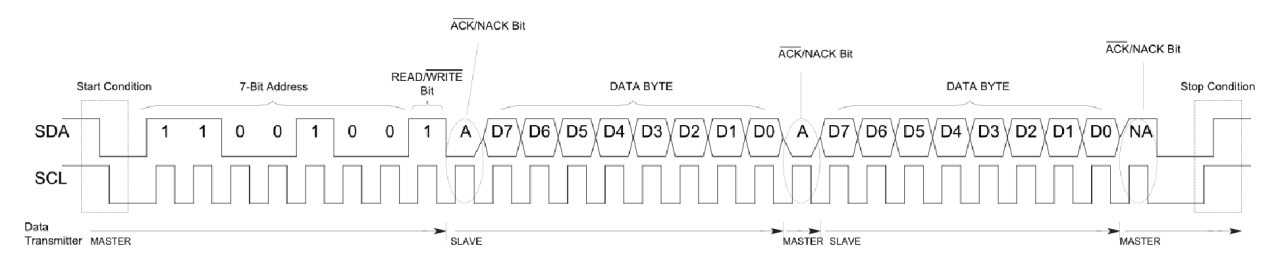

Figura 4: Condición de inicio seguida de una dirección de 7 bits de 0 × 64 y un conjunto de comandos de escritura. El esclavo responde con un reconocimiento.

Un MAESTRO también enviará un NACK después del último byte de la transmisión que quiere leer de un ESCLAVO para indicar que el ESCLAVO debe detener la transmisión.

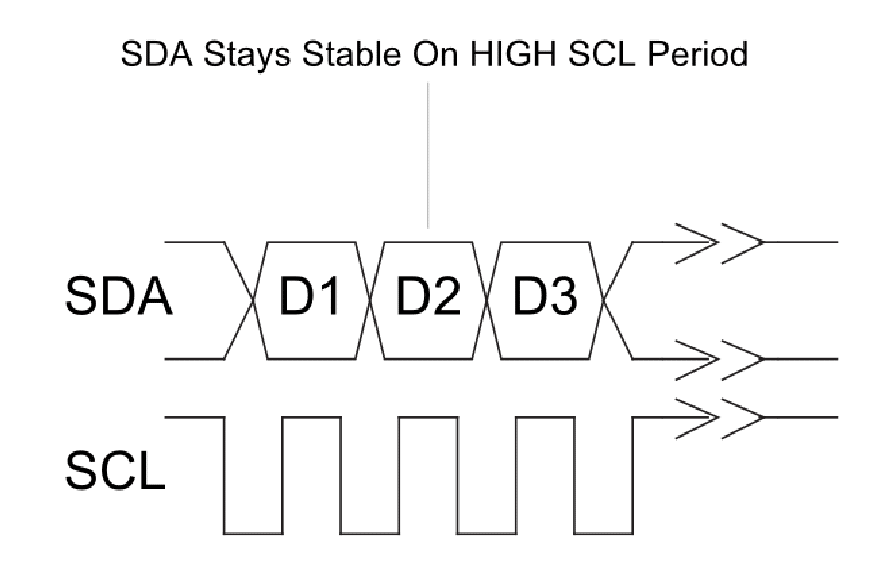

Los bits de datos codifican los datos de transmisión reales y se transmiten en formato de byte de 8 bits, comenzando con el MSB, y cada bit se sincroniza con la señal de reloj (SCL). No hay límite para el número de bytes en una transmisión, pero cada byte debe ir seguido de un Reconocimiento generado por el destinatario de los datos.

Figura 5: Transición de bits de bits de datos

Para una transferencia de bits, los datos en la línea SDA deben permanecer estables durante un período de reloj ALTO. La línea de datos puede tener una transición ALTA o BAJA solo cuando la señal del reloj es BAJA. Por lo tanto, el receptor lee un bit de datos en la línea de datos mientras SCL está ALTO y el transmisor afirma cada nuevo bit de datos mientras SCL está BAJO.

Al escribir o leer de un registro específico en un ESCLAVO, el maestro primero debe apuntar al registro específico escribiendo la dirección del registro una vez que se haya direccionado el ESCLAVO. Si bien la dirección de registro puede considerarse un byte de datos, para evitar confusiones, a menudo se clasifica como un byte de comando. Consulte las Figuras 6 y 7 como ejemplo.

La figura 6 muestra el direccionamiento de un transmisor MAESTRO y la escritura de datos en un receptor ESCLAVO con una dirección de 7 bits. El primer bit enviado es el bit START que inicia las comunicaciones. El byte de dirección sigue a los pulsos de reloj subsiguientes. En este momento, todos los dispositivos SLAVE en el bus están escuchando su dirección de dispositivo, que constituye los primeros siete bits del byte de dirección. El dispositivo SLAVE que encuentra una coincidencia de dirección continúa escuchando el último bit (bit READ/WRITE#) para comprender si el maestro desea leer del esclavo o escribir en él. Todos los demás dispositivos SLAVE ignoran la comunicación adicional enviando un NACK, que por definición no hace nada.

Figura 6: Transmisión exitosa de bytes de escritura I2C

En respuesta al reconocimiento de su dirección y el comando de escritura, el dispositivo direccionado responde enviando un bit de reconocimiento (ACK) como retroalimentación al MAESTRO de que un dispositivo ESCLAVO con la dirección correcta está presente en el bus y esperando más comunicación. El MAESTRO luego procede con la transferencia de datos enviando datos en formato de byte. Si el MAESTRO está escribiendo en un registro específico en el dispositivo ESCLAVO, entonces escribe el byte de Comando correspondiente antes de enviar los datos. Después de cada transferencia de bytes, el ESCLAVO responde enviando un ACK. Una vez que el MAESTRO termina de transferir todos los datos, finaliza la transferencia enviando una condición de PARADA.

La figura 7 muestra un MAESTRO dirigiéndose a un ESCLAVO e intentando leer datos de él. El MAESTRO inicia nuevamente la transmisión con una condición de INICIO, después de lo cual la dirección se transmite en pulsos de reloj subsiguientes. El dispositivo direccionado continúa escuchando la transmisión leyendo el bit de LECTURA/ESCRITURA y responde con un bit de reconocimiento. Una vez que el ESCLAVO envía el reconocimiento, asume el control de SDA y envía datos al MAESTRO. En respuesta a cada byte transmitido, el MAESTRO envía un bit de reconocimiento. Cuando el MAESTRO ya no quiere recibir datos, responde con un NACK después del último byte que desea recibir y luego reanuda el control del bus y envía una condición de STOP para finalizar la transmisión.

Tenga en cuenta que mientras el control de la línea SDA se pasa de MAESTRO a ESCLAVO y viceversa, la línea SCL SIEMPRE tiene el control del MAESTRO, es decir, el MAESTRO registra la entrada y la salida de datos en todo momento.

Figura 7: Exitoso I2Transmisión de lectura C

Es posible combinar los protocolos de lectura y escritura en diferentes variaciones para realizar algunos I complejos2transacciones C. El MAESTRO puede escribir, luego leer desde el mismo esclavo o dar una nueva dirección para hablar con un dispositivo ESCLAVO diferente dentro de un solo I2transacción C, los datos pueden cambiar de dirección de modo que un dispositivo en el que se estaba escribiendo ahora esté leyendo datos. Todo esto se logra mediante el uso de un bit de inicio repetido.

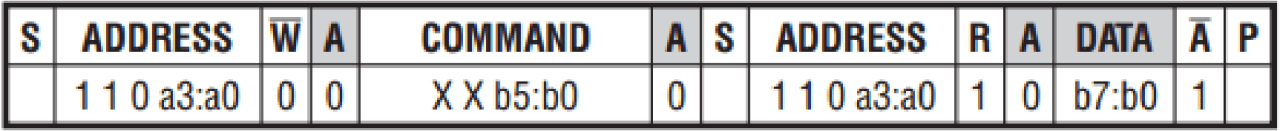

Por ejemplo, al LTC2946, que es un monitor de energía, se le puede ordenar que emita datos desde un registro específico. Esto requiere un yo2Transacción C que primero se dirige al LTC2946, envía un byte de comando (byte de datos que contiene una dirección de registro específica para leer), realiza un inicio repetido, envía la dirección del dispositivo nuevamente con el bit READ establecido y luego lee los datos. En esta transacción, primero el maestro estaba escribiendo en el LTC2946, diciéndole de qué registro quería leer los datos y luego el flujo direccional de los datos cambió cuando el MAESTRO realizó un inicio repetido con el bit de LECTURA establecido en el byte de dirección ESCLAVO. La Figura 8 se toma de la hoja de datos LTC2946 y muestra este protocolo general.

Figura 8: Protocolo de lectura de bytes SDA de bus serie LTC2946

Dónde

- S = Bit de inicio

- P = Bit de parada

- R = bit de lectura

- W\ = bit de escritura

- A = Reconocer

- A\ = No reconocer

La Figura 9 muestra un ejemplo de escritura en un registro en LTC2946. Después de la condición de inicio, se envía la dirección del dispositivo y luego se escribe el byte de comando en el esclavo (observe el bit READ/WRITE#). Una vez que el esclavo reconoce, los datos se escriben en el ESCLAVO.

Figura 9: Maestro escribiendo secuencialmente a dos esclavos diferentes

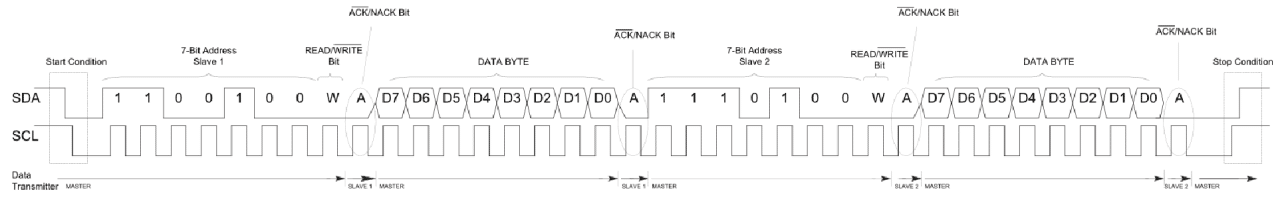

De manera similar, la Figura 10 muestra un ejemplo en el que el maestro escribe a dos esclavos diferentes.

Figura 10: Maestro escribiendo secuencialmente a dos esclavos diferentes

Hay yo adicional2Protocolos C como Comando rápido, Modo de dirección extendida, Arbitraje, Multi-Master y Clock Stretching que no tocamos en este artículo. Estos temas están más allá del alcance de la discusión de esta publicación de blog y no son necesarios para comenzar a comunicarse con un dispositivo LTC compatible con I2C.

Si quieres conocer otros artículos parecidos a Introducción a I2C: ¿Qué es I2C? (Parte 1) puedes visitar la categoría Generalidades.

Deja una respuesta

¡Más Contenido!