Los aceleradores de hardware aumentan el rendimiento de los procesadores SHARC de nueva generación

Resumen

El SHARC de Analog Devices ha anunciado recientemente® El procesador ADSP-2146x incorpora aceleradores de hardware para implementar tres operaciones de procesamiento de señales muy utilizadas: FIR (respuesta al impulso finita), IIR (respuesta al impulso infinita) y FFT (transformada rápida de Fourier). Los aceleradores descargan el procesador central y tienen el potencial de duplicar el rendimiento computacional del procesador. Este artículo presenta los aceleradores tomando como ejemplo su aplicación en los sistemas de audio de nueva generación.

Por qué los aceleradores de hardware

Los filtros FIR, los filtros IIR y las operaciones FFT tan utilizadas en el procesamiento digital de señales tienen una estructura regular que permite su implementación directa en hardware, concretamente en aceleradores de hardware. Estos aceleradores son dispositivos dedicados, de función fija, diseñados para realizar una única tarea computacionalmente intensiva una y otra vez. Quitan la carga al procesador principal, permitiéndole realizar tareas de uso general con poca estructura regular.

El uso de aceleradores de hardware ofrece una forma rentable de aumentar la potencia de cálculo global de un procesador, ya que el diseñador del sistema se beneficia de la flexibilidad de un procesador de propósito general junto con la ventaja de cálculo del hardware dedicado.

Por ello, estos aceleradores son un activo valioso para satisfacer las demandas de sistemas cada vez más complejos en muchas áreas de aplicación. Uno de ellos son los sistemas de audio, en los que el número de canales aumenta constantemente. Los sistemas de cine en casa han pasado de 5.1 canales, a 6.1, y ahora a 7.1 canales. Los amplificadores de gama alta para automóviles suelen utilizar 12 o más altavoces para sumergir al oyente en el sonido.

Además, ahora hay material de origen de audio en formatos de alta definición (HD) cuyos descodificadores asociados estiran los recursos del sistema. Además, los algoritmos HD proporcionan contenidos a una mayor frecuencia de muestreo. Antes, la frecuencia de muestreo máxima de los contenidos rara vez era superior a 48 kHz. Con los algoritmos de alta definición, la frecuencia de muestreo suele ser de 96 kHz y, en algunos casos, puede llegar a 192 kHz.

Para entender mejor cómo aumentan las exigencias computacionales, considera los receptores de cine en casa avanzados que incorporan sofisticados algoritmos de ecualización de la sala. Estos algoritmos compensan las variaciones en la respuesta de los transductores y la colocación de los altavoces. Los algoritmos analizan primero la sala mediante un micrófono y mediciones de la función de transferencia en tiempo real. Las mediciones de varios lugares se combinan de forma inteligente, y luego se diseña un filtro de compensación para cada altavoz.

Los algoritmos de ecualización de salas más precisos utilizan filtros FIR para corregir la respuesta en toda la gama de frecuencias. La longitud del filtro necesaria es directamente proporcional a la frecuencia de muestreo, y se necesitan filtros más largos para un control preciso de las bajas frecuencias. Las longitudes de filtro de 256 puntos son habituales a 48 kHz, mientras que para conseguir la misma resolución de frecuencia a 96 kHz, se requiere una longitud de filtro de 512 puntos. Esta duplicación de la frecuencia de muestreo y de la longitud de los filtros multiplica por cuatro la cantidad de cálculos necesarios.

Aceleradores en el SHARC ADSP-2146x

Los procesadores SHARC de Analog Devices tienen un largo historial de permitir una sofisticada funcionalidad de procesamiento de señales en multitud de aplicaciones. El núcleo y los periféricos ricos en funciones de estos procesadores los han convertido en una opción lógica para los desarrolladores de productos. El procesador SHARC ADSP-2146x de Analog Devices, presentado recientemente, refuerza esta posición de liderazgo con una mayor velocidad de reloj (450 MHz) y una memoria integrada ampliada (5 MB).

Además, el procesador está equipado con un conjunto de aceleradores de hardware para implementar operaciones comunes de procesamiento de señales: filtros FIR, filtros IIR y FFT. Estas operaciones constituyen la base de los sistemas de comunicación, los dispositivos médicos, los productos de consumo y las aplicaciones industriales de medición y control. Estos aceleradores complementan el convertidor de frecuencia de muestreo integrado, que se introdujo en el procesador SHARC ADSP-2136x, y también puede considerarse un acelerador de hardware.

Arquitectura del acelerador

Los tres aceleradores del SHARC ADSP-2146x tienen un diseño similar, por lo que el acelerador FIR que se muestra a continuación es una buena ilustración de la arquitectura del acelerador de hardware. El acelerador FIR tiene los siguientes componentes:

- Conjunto de registros de control: configura el funcionamiento del acelerador.

- Controlador DMA: mueve los datos entre la memoria principal y la memoria local del acelerador. También se puede utilizar para configurar los registros de control.

- Dos bloques de memoria local: almacenan los coeficientes y las variables de estado (o memoria de retardo), y reducen el ancho de banda hacia la memoria principal.

- Unidad de cálculo: contiene operaciones aritméticas adaptadas al acelerador. La unidad de cálculo FIR tiene cuatro MACs paralelos.

El funcionamiento del acelerador se automatiza mediante DMAs encadenados. El acelerador FIR suele pasar por los siguientes pasos:

- Carga los datos de los coeficientes de ese canal desde la memoria interna al almacenamiento de coeficientes del acelerador local.

- Carga las variables de estado de este canal desde la memoria interna al almacenamiento de variables de estado del acelerador local. Esto incluye la primera muestra de entrada.

- Calcula la muestra de salida utilizando las cuatro unidades MAC.

- Almacena el resultado.

- Si todavía hay muestras que procesar, busca la siguiente muestra de entrada y escribe en el almacenamiento de la variable de estado.

- Repite los pasos 3 a 5 hasta calcular todas las muestras de salida del canal.

- Repite los pasos 1 a 6 para todos los canales de entrada.

El núcleo ADSP-2146x tiene una velocidad de reloj máxima de 450 MHz. Utilizando SIMD (instrucción única de datos múltiples), el núcleo puede realizar dos operaciones MAC (multiplicar-acumular) por ciclo de reloj a una velocidad máxima de 900 MMAC/seg. El acelerador, en comparación, funciona a la velocidad de reloj del dispositivo SHARC de 225 MHz. Utilizando sus cuatro unidades MAC dedicadas, el acelerador FIR alcanza una tasa máxima teórica de 900 MMAC/seg. La configuración de los registros de control del acelerador FIR y el movimiento de los datos dentro y fuera de la memoria local conllevan cierta sobrecarga.

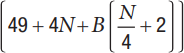

El número total de ciclos de reloj periféricos necesarios para implementar un determinado filtro FIR viene dado por la siguiente fórmula

donde N es el número de tomas del filtro y B es el tamaño del bloque. El número de ciclos puede descomponerse en :

49 = Inicialización del bloque de control de transferencia DMA.

4N = coeficiente de carga y valores de estado (línea de retardo) suponiendo dos ciclos por carga.

= ciclos para calcular una muestra de salida de un filtro NFIR de longitud.

Uso de aceleradores en la práctica

El software de aplicación debe diseñarse para aprovechar al máximo los aceleradores de hardware. Recuerda que los aceleradores deben estar configurados para ejecutarse en paralelo con la CPU principal, ya que no hay ninguna ventaja si la CPU principal está inactiva mientras espera que los aceleradores terminen.

Los aceleradores suelen formar parte de una cadena de señales más amplia que funciona en un entorno de tiempo real. La interconexión con los aceleradores requiere datos de entrada y salida con doble buffer, y el diseñador del sistema debe tener en cuenta que los aceleradores introducen un bloque de latencia.

Considera un sistema de cine en casa con 7,1 canales de audio de 96 kHz que funciona con un tamaño de bloque de 32 muestras. Supongamos que la ecualización de la sala se aplica mediante ocho filtros FIR de 512 puntos cada uno. Si el procesador central realizara el filtrado, necesitaría al menos 96 kHz × 8 × 512 = 393 MMAC/seg, o el 44% de un procesador SHARC de 450 MHz. Este procesamiento FIR es una parte importante del cálculo global y, afortunadamente, puede descargarse en el acelerador. Las entradas y salidas de los filtros FIR tienen doble búfer, lo que permite que el acelerador funcione en paralelo con el resto de la cadena de señales de audio. El doble buffering introduce 32 muestras de retardo en el procesamiento, lo que supone un retardo aceptable de 333 μs a 96 kHz.

Utilizando la fórmula anterior, el acelerador necesita 50.056 ciclos periféricos para realizar la operación. A una velocidad de 225 MHz, esto representa 223 μs, lo que está bien dentro del tiempo de bloque de 333 μs.

Conclusión

Los continuos avances en la tecnología de procesamiento de audio exigen cada vez más a los DSP de audio. Los aceleradores de hardware del procesador SHARC ADSP-2146x de nueva generación permiten un aumento significativo de la potencia de procesamiento global. Los aceleradores descargan las operaciones rutinarias de procesamiento de señales -filtros IR, filtros IIR y operaciones FFT- del núcleo del procesador, permitiéndole concentrarse en otras tareas. Este enfoque rentable duplica con creces el rendimiento computacional del procesador. Aunque este artículo se centra en aplicaciones de audio, el núcleo y los aceleradores son versátiles y se adaptan bien a diversas tareas de procesamiento de señales.

Si quieres conocer otros artículos parecidos a Los aceleradores de hardware aumentan el rendimiento de los procesadores SHARC de nueva generación puedes visitar la categoría Generalidades.

Deja una respuesta

¡Más Contenido!