Interfaz a convertidores seriales - 1

P. Necesito convertidores de datos que quepan en un espacio reducido y sospecho que una interfaz en serie me ayudará. ¿Qué necesito saber para elegir y usar uno?

UNA. Comencemos observando cómo funciona una interfaz serial y luego compárela con una interfaz paralela. Al hacer esto, disiparemos algunos mitos sobre los convertidores de datos en serie.

La figura muestra un convertidor A/D (ADC) serie de 12 bits multiplexado de 8 canales AD7890 conectado al puerto serie de un procesador de señal digital (DSP) ADSP-2105. También se muestra la secuencia de tiempo que utiliza el DSP para comunicarse con el ADC. Los 12 bits que constituyen el resultado de la conversión se transmiten como un flujo de datos en serie a través de una sola línea. El flujo de datos también incluye tres bits adicionales que identifican el canal de entrada que el multiplexor del AD7890 está seleccionando actualmente. Para distinguir los bits del flujo de datos en serie entre sí, se debe proporcionar una señal de reloj (SCLK), generalmente por parte del DSP; Sin embargo, a veces el ADC suministra este reloj como salida. El DSP generalmente (pero no siempre) proporciona un pulso de trama adicional que está activo durante un ciclo al comienzo de la comunicación o, como se muestra (TFS/RFS), durante la duración de la transmisión.

En este ejemplo, el puerto serial del DSP se usa para programar un registro interno de 5 bits en el ADC. Los bits del registro controlan funciones tales como seleccionar el canal a convertir, poner el dispositivo en modo de apagado e iniciar una conversión. Debe ser evidente que la interfaz serial, en este caso, debe ser bidireccional.

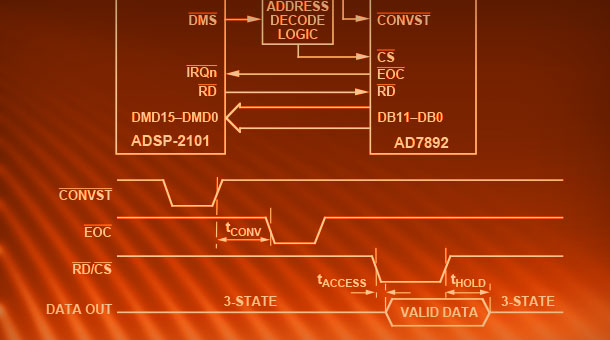

Un ADC paralelo, por otro lado, se conecta directamente (o posiblemente a través de búferes) al bus de datos del procesador con el que está conectado. La figura muestra el AD7892 conectado a un ADSP-2101. Cuando se completa una conversión, el AD7892 interrumpe el DSP, que responde haciendo una sola lectura de la dirección de memoria decodificada del ADC.

La diferencia clave entre los convertidores de datos en serie y en paralelo radica en la cantidad de líneas de interfaz requeridas. Desde el punto de vista del ahorro de espacio, los convertidores en serie ofrecen una clara ventaja debido a la reducción del número de pines del dispositivo. Esto hace posible empaquetar un ADC o DAC serial de 12 bits en un paquete DIP o SO de 8 pines. Más significativamente, se ahorra espacio en la placa porque las conexiones de interfaz en serie requieren menos pistas de PCB.

P. Mis convertidores de digital a analógico tienen que estar físicamente alejados del procesador central y entre sí. ¿Cuál es la mejor manera de abordar esto?

UNA. Inicialmente, debe decidir si usar DAC en serie o en paralelo. Con los DAC paralelos, puede asignar cada uno a una ubicación de E/S asignada a la memoria, como se muestra en la figura. Luego programaría cada DAC simplemente haciendo un comando de escritura en la ubicación de E/S adecuada. Sin embargo, esta configuración tiene una desventaja significativa. Requiere un bus de datos paralelo, junto con algunas señales de control, a todas las ubicaciones remotas. Claramente, una interfaz serial, que puede tener tan solo dos cables, es mucho más económica.

En general, los convertidores en serie no se pueden asignar a la memoria de un procesador. Pero se podrían conectar varios DAC en serie al puerto de E/S en serie del procesador. Luego, se podrían usar otros puertos en el procesador para generar señales Chip Select para habilitar los DAC individualmente. Las señales Chip Select requerirán una línea desde cada dispositivo hasta la interfaz. Pero puede haber un límite en la cantidad de líneas en el procesador que se pueden configurar para transmitir señales Chip Select.

Una forma de solucionar este problema es usar DAC en serie que se pueden conectar en cadena. La figura muestra cómo conectar varios DAC a un solo puerto de E/S. Cada DAC tiene un pin de salida de datos en serie (SDO) que se conecta al pin de entrada de datos en serie (SDI) del siguiente DAC en la cadena. LDAC y SCLK se alimentan en paralelo a todos los DAC de la cadena. Debido a que los datos registrados en SDI finalmente aparecen en SDO (N ciclos de reloj más tarde), un solo puerto de E/S puede abordar varios DAC. Sin embargo, el puerto debe generar un flujo de datos largo (N bits por DAC multiplicado por la cantidad de dispositivos en la cadena). La gran ventaja de esta configuración es que no se necesita la decodificación del dispositivo. Todos los dispositivos están efectivamente en la misma ubicación de E/S. El principal inconveniente de la conexión en cadena es la accesibilidad (o latencia). Para cambiar el estado de incluso un solo DAC, el procesador aún debe generar un flujo de datos completo desde el puerto de E/S.

P. Si los convertidores de datos en serie ahorran tanto espacio y cableado, ¿por qué no se utilizan en todas las aplicaciones sensibles al espacio?

UNA. Una desventaja importante de la interfaz en serie es la compensación de velocidad por espacio. Por ejemplo, para programar un DAC paralelo, simplemente coloque los datos en el bus de datos y regístrelos en el DAC con un solo pulso. Sin embargo, cuando se escribe en un DAC serial, los bits deben sincronizarse secuencialmente (N pulsos de reloj para un convertidor de N bits) y seguidos por un pulso de carga. El puerto de E/S del procesador pasa una cantidad relativamente grande de tiempo comunicándose con un convertidor serial. En consecuencia, los convertidores en serie con tasas de rendimiento superiores a 500 ksps son poco comunes.

P. Mi procesador de 8 bits no tiene un puerto serie. ¿Hay alguna forma de conectar un ADC serial de 12 bits como el AD7893 al bus paralelo del procesador?

R. Por supuesto, se puede hacer usando un registro de desplazamiento externo, que se carga en serie (y asíncronamente), y luego se sincroniza en el puerto paralelo del procesador. Sin embargo, si el sentido de la pregunta es "sin lógica externa", el ADC serial puede interconectarse como si fuera un ADC paralelo de 1 bit. Conecte el pin SDATA del convertidor a una de las líneas de bus de datos del procesador (está conectado a D0 en el diagrama). Usando alguna lógica de decodificación, el convertidor se puede asignar a una de las ubicaciones de memoria del procesador para que el resultado de la conversión se pueda leer con 12 comandos de lectura sucesivos. Luego, los comandos de software adicionales integran los LSB de los 12 bytes que se leyeron en una sola palabra paralela de 12 bits.

Esta técnica, que a veces se denomina "bit banging", es muy ineficaz desde la perspectiva del software. Pero puede ser aceptable en aplicaciones en las que el procesador funciona mucho más rápido que el convertidor.

P. En el último ejemplo, se utilizó una versión cerrada de la señal de escritura del procesador para iniciar las conversiones en el AD7893. ¿Hay problemas con ese enfoque?

UNA. Me alegro de que hayas notado eso. En este ejemplo, se puede iniciar una conversión haciendo una escritura ficticia en la ubicación de memoria asignada del AD7893. No se intercambian datos, pero el procesador proporciona el pulso de escritura necesario para comenzar la conversión. Desde una perspectiva de hardware, esta configuración es muy simple porque evita la necesidad de generar una señal de conversión. Sin embargo, la técnica no se recomienda en aplicaciones de adquisición de datos de CA, en las que las señales deben muestrearse periódicamente. Incluso si el procesador está programado para realizar escrituras periódicas en el ADC, la fluctuación de fase en el pulso de escritura degradará seriamente la relación señal-ruido (SNR) alcanzable. El proceso de activación puede hacer que la señal de escritura fluctúe aún peor. Un nivel de fluctuación de fase de reloj de muestreo de tan solo 1 ns, por ejemplo, degradaría la SNR de una onda sinusoidal ideal de 100 kHz a aproximadamente 60 dB (menos de 10 bits efectivos de resolución). También existe el peligro adicional de que el sobreimpulso y el ruido en la señal de muestreo degraden aún más la integridad de la conversión de analógico a digital.

P. ¿Cuándo debo elegir un convertidor con una interfaz serial asíncrona?

UNA. Un enlace asíncrono permite que los dispositivos intercambien datos sin reloj entre sí. Los dispositivos deben programarse inicialmente para utilizar los mismos formatos de datos. Esto implica establecer una velocidad de datos particular (generalmente expresada en baudios o bits por segundo). También es necesaria una convención que defina cómo iniciar y finalizar transmisiones. Hacemos esto usando secuencias de datos identificables llamadas comienzo y deténgase pedacitos La transmisión también puede incluir bits de paridad que facilitan la detección de errores.

La figura muestra cómo el acondicionador de señal digitalizador AD1B60 interactúa con el puerto COM asíncrono de una PC. Esta es una interfaz bidireccional de 3 hilos (las líneas de tierra se han omitido para mayor claridad). Observe que las líneas de recepción y transmisión intercambian roles en el otro extremo de la línea.

Un enlace de datos asíncrono es útil en aplicaciones en las que los dispositivos se comunican solo esporádicamente. Dado que los bits de inicio y parada se incluyen en cada transmisión, un dispositivo puede iniciar la comunicación en cualquier momento simplemente enviando sus datos. El número de conexiones entre dispositivos se reduce porque las señales de reloj y control ya no son necesarias.

P. La hoja de datos de un ADC que estoy considerando recomienda usar un reloj no continuo en la interfaz serial. ¿Por qué?

UNA. La especificación probablemente requiere que el reloj se mantenga inactivo mientras se realiza la conversión. Algunos ADC requieren esto porque un reloj de datos continuo puede pasar a la sección analógica del dispositivo y afectar negativamente la integridad de la conversión. Una señal de reloj continua puede interrumpirse durante la conversión si el puerto de E/S tiene un pulso de trama; se utiliza como una señal de puerta que habilita el reloj en serie al convertidor solo durante la transferencia de datos.

P. ¿Qué hace que un dispositivo sea compatible con SPI o MICROWIRE?

UNA. SPI (Interfaz periférica en serie) y MICROWIRE son estándares de interfaz en serie desarrollados por Motorola y National Semiconductor, respectivamente. La mayoría de los convertidores seriales síncronos se pueden conectar fácilmente a estos puertos; pero en algunos casos puede ser necesaria una lógica de "pegamento" adicional.

QOK Decidí dejar de lado los prejuicios y usar un ADC en serie en mi diseño actual. Acabo de conectarlo como especifica la hoja de datos. Cuando mi micro lee el resultado de la conversión, el ADC siempre parece generar FFFHEX. ¿Qué esta pasando?

UNA. Quizás tenga un problema de comunicación. Necesitamos observar las conexiones entre el ADC y el procesador, y cómo se han configurado las señales de tiempo y control. También tenemos que mirar la estructura de Interrupción. La próxima entrega volverá a este tema, discutiendo los problemas encontrados al diseñar interfaces seriales.

Si quieres conocer otros artículos parecidos a Interfaz a convertidores seriales - 1 puedes visitar la categoría Generalidades.

Deja una respuesta

¡Más Contenido!