El ABC de las CAN entrelazadas

Introducción

En muchos segmentos del mercado actual, el intercalado de convertidores analógico-digitales (ADC) ofrece varias ventajas en muchas aplicaciones. En la infraestructura de las comunicaciones, hay una presión constante para que los ADCs tengan una mayor velocidad de muestreo para permitir radios multibanda y multiportadora, además de los requisitos de mayor ancho de banda para las técnicas de linealización, como la predistorsión digital (DPD). En el ámbito militar y aeroespacial, los ADC de mayor frecuencia de muestreo permiten sistemas versátiles que pueden utilizarse para las comunicaciones, la vigilancia electrónica y el radar, por nombrar algunos. En la instrumentación industrial, la necesidad de ADCs de mayor velocidad de muestreo es cada vez mayor para poder medir señales más rápidas de forma correcta y precisa.

En primer lugar, es importante entender exactamente qué son los ADC intercalados. Para entender la intercalación, es bueno ver lo que realmente ocurre y cómo se implementa. Con una comprensión básica, se pueden discutir las ventajas de la intercalación. Por supuesto, como muchos saben, no hay almuerzo gratis, así que hay que evaluar y valorar los retos de la intercalación.

Sobre la intercalación

Cuando los ADC están intercalados, se utilizan dos o más ADC con una relación de reloj definida para muestrear simultáneamente una señal de entrada y producir una señal de salida combinada que da un ancho de banda de muestreo a algún múltiplo de los ADC individuales. Utilizando m número de ADC aumenta la frecuencia de muestreo efectiva en un factor de m. Para simplificar y facilitar la comprensión, nos centraremos en el caso de dos CAD. En este caso, si dos ADC, cada uno con una frecuencia de muestreo de fSse intercalan, la frecuencia de muestreo resultante es simplemente 2× fS. Estos dos ADCs deben tener una relación de fase de reloj para que el intercalado funcione correctamente. La relación de fase del reloj se rige por la ecuación 1, donde n es el CAD específico y m es el número total de ADCs.

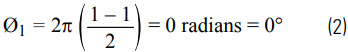

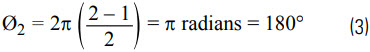

Como ejemplo, dos ADCs cada uno, con una frecuencia de muestreo de 100 MSPS, se intercalan para obtener una frecuencia de muestreo de 200 MSPS. En este caso, la ecuación 1 puede utilizarse para derivar la relación de fase de reloj de los dos ADC y viene dada por la ecuación 2 y la ecuación 3.

Ahora que se conoce la relación de la fase del reloj, se puede examinar la construcción de la muestra. La figura 1 ofrece una representación visual de la relación de la fase del reloj y la construcción de la muestra de dos ADC intercalados de 100 MSPS. Observa la relación de fase de reloj de 180° y cómo se intercalan las muestras. La forma de onda de entrada es muestreada alternativamente por los dos ADC. En este caso, el intercalado se realiza utilizando una entrada de reloj de 200 MHz que se divide por un factor de dos y las fases de reloj necesarias para cada ADC.

Figura 1: Esquema básico de dos ADC intercalados de 100 MSPS.

Otra representación de este concepto se muestra en la Figura 2. Al intercalar estos dos ADC de 100 MSPS, la velocidad de muestreo aumenta a 200 MSPS. Esto amplía cada zona de Nyquist de 50 MHz a 100 MHz, duplicando así el ancho de banda disponible para operar. El aumento del ancho de banda operativo aporta muchas ventajas a las aplicaciones de muchos segmentos del mercado. Los sistemas de radio pueden aumentar el número de bandas soportadas, los sistemas de radar pueden mejorar la resolución espacial y los equipos de medición pueden conseguir un mayor ancho de banda de entrada analógica.

Figura 2. Dos ADC intercalados de 100 MSPS: bloqueo y muestras.

Ventajas de la intercalación

Las ventajas de la intercalación se refieren a varios segmentos del mercado. La ventaja más deseada del intercalado es el aumento del ancho de banda que permite la zona de Nyquist más amplia de los ADC intercalados. De nuevo, utilizando el ejemplo de dos ADC de 100 MSPS intercalados para crear una velocidad de muestreo de 200 MSPS, la Figura 3 ofrece una representación del ancho de banda mucho mayor que permite el intercalado de los dos ADC. Esto crea ventajas para muchas aplicaciones diferentes. A medida que los estándares celulares aumentan el ancho de banda del canal y el número de bandas operativas, aumentan las demandas de ancho de banda disponible en el ADC. Además, en las aplicaciones militares, los requisitos para un mejor reconocimiento espacial, así como el aumento del ancho de banda del canal en las comunicaciones troncales, requieren mayores anchos de banda del ADC. Debido a la mayor demanda de ancho de banda en estas áreas, es necesario medir estas señales con precisión. Por lo tanto, los equipos de medición han aumentado los requisitos de los anchos de banda más elevados para poder adquirir y medir correctamente estas señales que tienen mayores anchos de banda. Los requisitos del sistema en muchos diseños siguen estando intrínsecamente por delante de la tecnología ADC comercial. La intercalación salva parte de este vacío.

Figura 3. Dos ADC intercalados - Zona de Nyquist.

El aumento de la frecuencia de muestreo proporciona más ancho de banda para estas aplicaciones, pero también facilita la planificación de la frecuencia y reduce la complejidad y el coste del filtro antialiasing que se suele utilizar en las entradas del ADC. Con todas estas ventajas, cabe preguntarse qué precio hay que pagar. Como en la mayoría de las cosas, no hay almuerzo gratis. Los ADCs intercalados ofrecen un mayor ancho de banda y otras atractivas ventajas, pero hay algunos retos cuando se utilizan ADCs intercalados.

Desafíos de la intercalación

Hay retos y cosas que hay que tener en cuenta cuando se intercalan ADCs. Hay picos que aparecen en el espectro de salida que se deben a las imperfecciones asociadas a los ADC intercalados. Estas imperfecciones son esencialmente desajustes entre los dos ADCs que se intercalan. Hay cuatro desajustes básicos que provocan llamaradas en el espectro de salida. Se trata de desajuste de desplazamiento, desajuste de ganancia, desajuste de temporización y desajuste de ancho de banda.

Probablemente lo más fácil de entender es el desajuste de offset entre los dos ADC. Cada ADC tendrá un valor de desplazamiento de CC asociado. Cuando los dos ADC se intercalan y las muestras se adquieren alternativamente entre los dos ADC, el desplazamiento dc de cada muestra sucesiva cambia. La figura 4 muestra un ejemplo de cómo cada ADC tiene su propio desplazamiento de CC y cómo la salida intercalada cambia realmente entre estos dos valores de desplazamiento de CC. La salida cambia entre estos valores de desplazamiento a una velocidad de fS/2, lo que dará lugar a un pico en el espectro de salida a fS/2. Como el propio desajuste no tiene componente de frecuencia y sólo está en cc, la frecuencia de espuela que aparece en el espectro de salida sólo depende de la frecuencia de muestreo y siempre aparecerá a una frecuencia de fS/2. El tamaño del espolón depende del tamaño del desajuste entre los ADC. Cuanto mayor sea el desajuste, mayor será el estímulo. Para minimizar el espolón causado por el desajuste del offset, no es necesario cancelar completamente el offset de CC en cada ADC. Esto filtraría cualquier contenido de CC en la señal y no funcionaría en los sistemas que utilizan una arquitectura de frecuencia intermedia cero (ZIF), donde el contenido de la señal es real y complejo e incluye datos de CC. En cambio, una técnica más adecuada sería hacer coincidir el desplazamiento de un ADC con el otro ADC. Se elige el desplazamiento de un ADC como referencia y se ajusta el desplazamiento del otro ADC para que coincida con este valor lo más posible. Cuanto más se ajusten los valores de desplazamiento, menor será el rebasamiento resultante en fS/2.

Figura 4: Desajuste de desplazamiento.

El segundo desajuste que hay que tener en cuenta al intercalar es el desajuste de ganancia entre los convertidores analógicos. La figura 5 muestra una representación del desajuste de ganancia entre dos convertidores intercalados. En este caso, hay un componente de frecuencia en el desajuste. Para observar este desajuste, hay que aplicar una señal a los convertidores analógicos. En el caso del desfase, no se necesita ninguna señal para ver el desfase de CC inherente a los dos convertidores analógicos. En el caso del desajuste de ganancia, no hay forma de ver el desajuste de ganancia a menos que haya una señal presente y se pueda medir el desajuste de ganancia. El desequilibrio de la ganancia dará lugar a un pico en el espectro de salida que está relacionado con la frecuencia de entrada, así como con la frecuencia de muestreo, y aparecerá en fS/2 ± fES. Para minimizar el espolón provocado por el desajuste de ganancia, se emplea una estrategia similar a la utilizada para el desajuste de desplazamiento. La ganancia de uno de los ADC se elige como referencia, y la ganancia del otro ADC se ajusta para que coincida con este valor de ganancia lo más posible. Cuanto más se ajusten los valores de ganancia de cada ADC, menos saltos habrá en el espectro de salida.

Figura 5. Desajuste de ganancia.

A continuación, tenemos que ver el desfase entre los dos convertidores analógicos. El desfase tiene dos componentes, el retardo de grupo en la sección analógica del ADC y el desfase del reloj. El circuito analógico del ADC tiene un retardo de grupo asociado y su valor puede ser diferente entre los dos ADC. Además, hay un desvío de reloj que tiene una componente de incertidumbre de apertura en cada uno de los ADC y que tiene una componente relacionada con la precisión de las fases de reloj que se introducen en cada convertidor. La figura 6 ofrece una representación visual del mecanismo y los efectos de la desviación del reloj en los ADC. Al igual que el pico de desincronización de la ganancia, el pico de desincronización de la temporización también es función de la frecuencia de entrada y de la frecuencia de muestreo y aparece en fS/2 ± fES.

Figura 6. Desajuste temporal.

Para minimizar el espolón resultante, el retardo de grupo a través de la sección analógica de cada convertidor debe ajustarse adecuadamente con buenas técnicas de diseño de circuitos. Además, los diseños de la trayectoria del reloj deben estar estrechamente adaptados para minimizar las diferencias en la incertidumbre de la apertura. Y, por último, las relaciones de fase de los relojes deben controlarse con precisión para que los dos relojes de entrada estén lo más cerca posible de 180°. Al igual que con los otros desplazamientos, el objetivo es tratar de minimizar los mecanismos que provocan el desplazamiento temporal.

El último desplazamiento que hay que tener en cuenta es probablemente el más difícil de entender y gestionar: es el desplazamiento del ancho de banda. Como se muestra en la figura 7, el desajuste del ancho de banda tiene una ganancia y un componente de fase/frecuencia. Esto dificulta el desajuste del ancho de banda porque contiene componentes de dos de los otros parámetros de desajuste. Sin embargo, en el desajuste del ancho de banda, vemos diferentes valores de ganancia en las distintas frecuencias. Además, el ancho de banda tiene un componente de temporización que hace que las señales a diferentes frecuencias tengan diferentes retrasos en cada convertidor. La mejor manera de minimizar el desajuste del ancho de banda es tener un diseño de circuito y unas prácticas de disposición muy buenas que minimicen el desajuste del ancho de banda entre los ADC. Cuanto mejor se adapte cada ADC, menor será el espurio. Al igual que los desajustes de ganancia y temporización provocaban picos en el espectro de salida a fS/2 ± fESel desplazamiento del ancho de banda también provoca un espolón en la misma frecuencia.

Figura 7: Desajuste del ancho de banda.

Ahora que hemos hablado de cuatro desajustes diferentes que causan problemas al intercalar los CAD, está claro que ha surgido un hilo conductor. Tres de los cuatro desajustes producen un pico en el espectro de salida a fS/2 ± fES. El espolón desplazado puede identificarse fácilmente, ya que reside solo en fS/2 y se puede compensar con bastante facilidad. Los desequilibrios de ganancia, temporización y ancho de banda producen un espolón a fS/2 ± fES por tanto, la cuestión es cómo identificar la contribución de cada uno. La figura 8 ofrece una guía visual rápida del proceso de identificación de las fuentes de los destellos a partir de los diferentes desplazamientos intercalados del CAD.

Figura 8. Naturaleza interdependiente de los desajustes de intercalación.

Si sólo se considera el desequilibrio de la ganancia, se trata de un tipo de desequilibrio de baja frecuencia, o dc. El componente de ganancia del desequilibrio de ancho de banda puede separarse del desequilibrio de ganancia haciendo una medición de ganancia de baja frecuencia cerca de cc, y luego haciendo mediciones de ganancia a frecuencias más altas. El desajuste de ganancia no es una función de la frecuencia, como el componente de ganancia del desajuste de ancho de banda. Se utiliza un enfoque similar para el desajuste temporal. Se realiza una medición a una frecuencia baja cercana a la CC, y luego se realizan mediciones posteriores a frecuencias más altas para separar el componente temporal del desajuste del ancho de banda del desajuste temporal.

Conclusión

Los últimos diseños de sistemas de comunicación, las tecnologías avanzadas de radar y los equipos de medición de banda ultraancha parecen superar constantemente la tecnología CAN disponible. Sus demandas empujan a los usuarios de la CAN y a los fabricantes a desarrollar métodos para seguir el ritmo de estas demandas. Intercalar ADCs permite conseguir mayores anchos de banda a un ritmo más rápido que la vía tradicional de aumentar la tasa de conversión de un ADC típico. Si se toman dos o más ADC y se intercalan, el ancho de banda disponible aumenta y los requisitos de diseño del sistema se pueden cumplir más rápidamente. Sin embargo, intercalar ADCs no es gratis, y no se pueden ignorar los desequilibrios entre ADCs. Aunque estos desajustes existan, ser conscientes de ellos y saber cómo tratarlos adecuadamente puede permitir a los diseñadores utilizar estos ADC intercalados de forma más inteligente y satisfacer las exigencias cada vez mayores de sus últimos diseños de sistemas.

Referencias

Had, Jim, Mark Looney y Rob Reeder. "Impulsando el estado del arte con convertidores A/D multicanal" Diálogo analógicovol. 39, nº 5, mayo de 2005.

Si quieres conocer otros artículos parecidos a El ABC de las CAN entrelazadas puedes visitar la categoría Generalidades.

Deja una respuesta

¡Más Contenido!