La verificación de redundancia cíclica garantiza comunicaciones de datos correctas

Los sistemas electrónicos que funcionan en entornos industriales a menudo deben soportar temperaturas extremas, entornos eléctricamente ruidosos u otras condiciones adversas; sin embargo, es fundamental que funcionen correctamente. Por ejemplo, si los datos enviados a un DAC que controla la posición de un brazo robótico se corrompieron, el brazo podría moverse en una dirección no deseada. Esto no solo podría ser peligroso sino costoso: imagine el brazo chocando contra el costado de un automóvil nuevo en una línea de producción o, peor aún, contra un trabajador de producción.

Hay varios métodos disponibles para garantizar que se hayan recibido los datos correctos antes de tomar medidas. La más simple es que el controlador vuelva a leer los datos que se enviaron. Si los datos recibidos no coinciden con los datos enviados, uno de ellos se ha dañado y se deben enviar y verificar nuevos datos. Este método es confiable, pero también conlleva una gran sobrecarga: cada dato debe verificarse, duplicando la cantidad de datos transferidos.

Una alternativa, comprobación de redundancia cíclica (CRC), es enviar un checksum con cada paquete de datos. El dispositivo receptor indicará si se ha producido un problema, por lo que el controlador no necesita verificar la recepción. Las sumas de verificación se generan comúnmente aplicando una ecuación polinomial a los datos. CRC-8 produce una suma de verificación de 8 bits cuando se aplica a una palabra de 24 bits. Combinar la suma de verificación con los datos, transmitir los 32 bits a un dispositivo que puede analizar la combinación e indicar los errores que ocurren, aunque no es una solución totalmente perfecta, es más eficiente que el método de escritura y lectura.

Muchos DAC de Analog Devices implementan CRC en forma de comprobación de errores de paquetes (PEC). Los datos de 24 bits se escriben cuando no se requiere la función PEC. Para agregar la función PEC, los datos de 24 bits se aumentan con una suma de verificación correspondiente de 8 bits. Si la suma de verificación recibida no concuerda con los datos, se baja un pin de salida para indicar el error. El controlador borra el error, devuelve el pin alto y vuelve a enviar los datos. La figura 1 muestra un ejemplo de cómo se aplican los datos mediante una interfaz SPI. La Tabla 1 enumera una muestra de piezas de Analog Devices que pueden usar la verificación de errores de paquetes.

Tabla 1. Ejemplos de piezas de dispositivos analógicos que utilizan la comprobación de errores de paquetes

| Número de parte | Descripción |

| AD5360/AD5361 | DAC de 16 canales, 16/14 bits, ±10 V |

| AD5362/AD5363 | DAC de 8 canales, 16/14 bits, ±10 V |

| AD5748 | Controlador de salida de corriente/voltaje industrial |

| AD5749 | Controlador de salida de corriente industrial |

| AD5750/AD5750-1 | Controladores industriales de salida de corriente/voltaje con rangos programables |

| AD5751 | Controlador de salida de corriente/voltaje industrial |

| AD5755/AD5735 | DAC de salida de voltaje y corriente de 4 mA a 20 mA de 4 canales, 16 bits |

| AD5757/AD5737 | DAC de salida de corriente de 4 canales, 16 bits, 4 mA a 20 mA |

| ADT7470 | Concentrador de sensor de temperatura y controlador de ventilador |

Generación de la suma de comprobación de errores del paquete

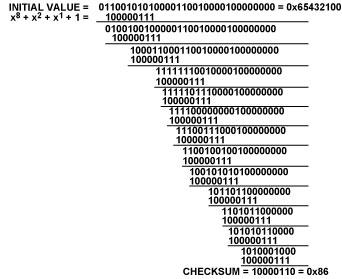

El algoritmo CRC-8 utiliza el polinomio C(x) = x8 + x2 + x1 + 1. para x = 2, esto es equivalente al valor binario 100000111. Para generar la suma de verificación, los datos de 24 bits se desplazan a la izquierda ocho bits para crear un número de 32 bits que termina en ocho 0 lógicos. El polinomio CRC se alinea de modo que su MSB esté adyacente al Lógico 1 más a la izquierda de los datos de 32 bits. Se aplica una función exclusiva o (XOR) a los datos para producir un número nuevo (más corto). (Los números que coinciden dan 0 lógico, los que no coinciden dan 1 lógico.) El polinomio CRC se alinea de nuevo para que su MSB esté adyacente al 1 lógico más a la izquierda del primer resultado, y se repite el procedimiento. Eventualmente, los datos originales se reducirán a un valor menor que el polinomio CRC. Esta es la suma de comprobación de 8 bits. La figura 2 demuestra cómo se desarrolla la suma de comprobación.

Conclusión

El ejemplo que se muestra en la Figura 2 usa el valor (hexadecimal) de 0x654321 como una palabra de datos de 24 bits de muestra. La aplicación del polinomio CRC-8 a los datos genera una suma de comprobación de 0x86. Cuando los datos y la suma de verificación se envían a un producto de Analog Devices compatible, los datos se aceptarán solo si ambos llegan correctamente. Este método aumenta la confiabilidad de las transferencias de datos y garantiza que casi nunca se acepten datos corruptos.

Si quieres conocer otros artículos parecidos a La verificación de redundancia cíclica garantiza comunicaciones de datos correctas puedes visitar la categoría Generalidades.

Deja una respuesta

¡Más Contenido!