Donde gana Zero-IF: un 50% menos de huella de PCB a ⅓ del coste

Introducción

La arquitectura Zero-IF (ZIF) existe desde los primeros tiempos de la radio. Hoy en día, la arquitectura ZIF se encuentra en casi todas las radios de consumo, desde los televisores hasta los teléfonos móviles y el Bluetooth® tecnología. La razón principal de esta amplia adopción es que ha demostrado repetidamente que ofrece el menor coste, la menor potencia y la menor huella de cualquier tecnología de radio. Históricamente, esta arquitectura ha sido rechazada para aplicaciones que requieren un alto rendimiento. Sin embargo, con la creciente demanda de tecnología inalámbrica que nos rodea y la rápida congestión del espectro, es necesario un cambio para seguir desplegando económicamente radios en la infraestructura que soporta nuestras necesidades inalámbricas. Las arquitecturas contemporáneas Zero-IF pueden satisfacer estas necesidades porque muchas de las degradaciones normalmente asociadas a estas arquitecturas se han resuelto mediante una combinación de proceso, diseño, partición y algoritmos. Los nuevos avances en la tecnología ZIF están desafiando a las actuales arquitecturas de radio de alto rendimiento e introduciendo nuevos productos con un rendimiento rompedor para permitir nuevas aplicaciones que antes estaban fuera del alcance de la ZIF. Este artículo explora las numerosas ventajas de las arquitecturas ZIF y presenta los nuevos niveles de rendimiento que aportan a los diseños de radio.

Los retos del ingeniero de radiocomunicaciones1

El arquitecto de transceptores de hoy se enfrenta a una lista creciente de requisitos relacionados con nuestras necesidades cada vez mayores de dispositivos y aplicaciones inalámbricas. Esto provoca la necesidad continua de acceder a más ancho de banda.

A lo largo de los años, el diseñador ha pasado de una radio de una sola portadora a una radio de varias portadoras. Cuando el espectro está totalmente ocupado en una banda, se asignan nuevas bandas; ahora hay más de 40 bandas inalámbricas que necesitan ser atendidas. Como los operadores tienen espectro en varias bandas y hay que coordinar estos recursos, la tendencia es hacia la agregación de portadoras, y la agregación de portadoras conduce a radios multibanda. Todo esto hace que haya más radios, con mayor rendimiento, que requieren un mejor rechazo fuera de banda, mejores emisiones y menor disipación de energía.

Aunque la demanda de tecnología inalámbrica crece rápidamente, los presupuestos de energía y espacio no lo hacen. De hecho, con una necesidad cada vez mayor de ahorrar energía y espacio, es muy importante reducir tanto la huella de carbono como la física. Para lograr estos objetivos, es necesario adoptar una nueva perspectiva sobre las arquitecturas de radio y la partición.

Integración

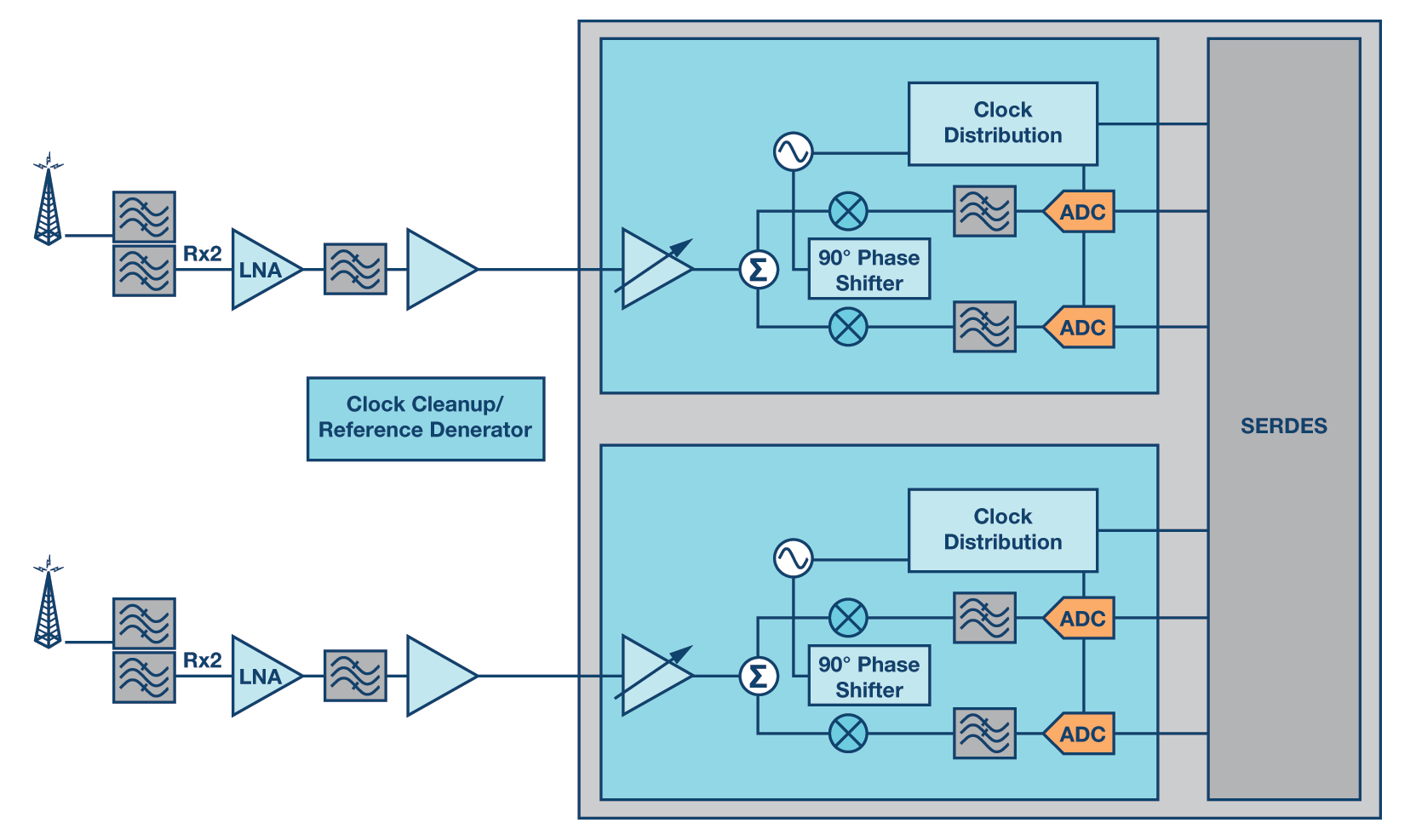

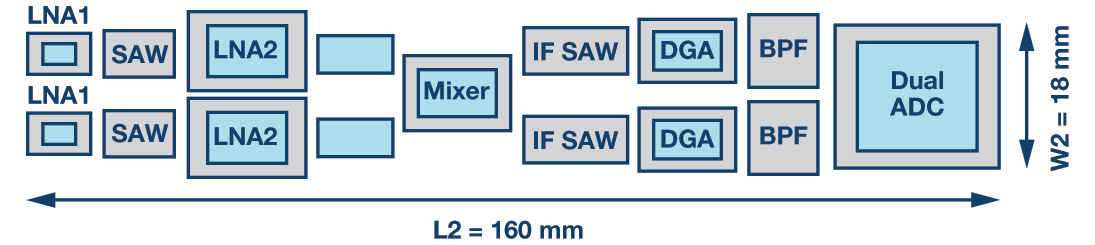

Para aumentar el número de radios en un diseño concreto, hay que reducir las huellas de cada radio. La forma tradicional de hacerlo es integrar progresivamente más y más del diseño en una sola pieza de silicio. Aunque esto puede tener sentido desde el punto de vista digital, integrar la funcionalidad analógica por el bien de la integración no siempre tiene sentido. Una de las razones es que muchas funciones analógicas de una radio no pueden integrarse eficazmente. Por ejemplo, en la figura 1 se muestra un receptor de muestreo de FI tradicional. Una arquitectura de muestreo de FI tiene cuatro pasos básicos: ganancia de bajo ruido y selectividad de RF, traslación de frecuencia, ganancia y selectividad de FI y detección. Para la selectividad, se suelen utilizar filtros SAW. Estos dispositivos no pueden integrarse y, por tanto, deben estar fuera del chip. Mientras que la selectividad de RF la proporcionan dispositivos piezoeléctricos o mecánicos, a veces se utilizan filtros LC para el filtro de FI. Aunque los filtros LC pueden integrarse a veces en estructuras monolíticas, la compensación del rendimiento del filtro (Q y pérdida de inserción) y el necesario aumento de la velocidad de muestreo del digitalizador (detector) aumentan la disipación global.

Los digitalizadores (convertidores analógico-digitales) deben fabricarse en procesos CMOS de bajo coste para mantener un coste y una potencia razonables. Aunque es cierto que se pueden fabricar en procesos bipolares, esto da lugar a dispositivos más grandes y que consumen más energía, lo que va en contra de la optimización del tamaño. Así que el CMOS estándar es el proceso deseado para esta función. Esto se convierte en un reto para la integración de amplificadores de alto rendimiento, especialmente la etapa de FI. Aunque los amplificadores pueden integrarse en procesos CMOS, es difícil obtener el rendimiento necesario a partir de procesos optimizados para baja potencia y baja tensión. Además, la integración del mezclador y el amplificador de FI en el chip requiere que las señales entre etapas se encaminen fuera del chip para acceder a los filtros de FI y antialiasing antes de ser digitalizadas, con lo que se renuncia a gran parte de las ventajas de la integración. Esto va en contra de la integración porque aumenta el número de pines y el tamaño del paquete. Además, siempre que las señales analógicas críticas pasan por una patilla del paquete, se produce un compromiso en el rendimiento.

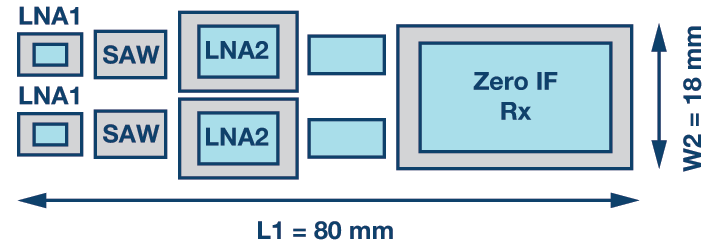

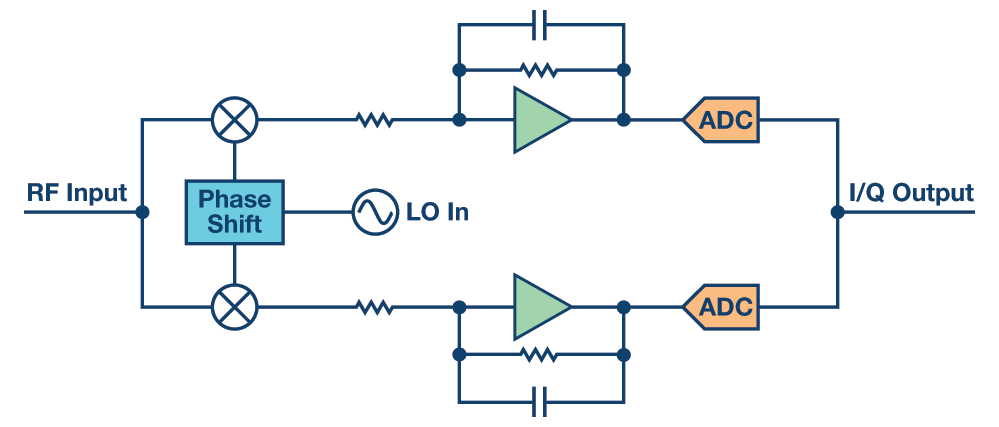

La forma óptima de integrar es desglosar el sistema para eliminar los elementos que no se pueden integrar. Dado que los filtros SAW y LC no pueden integrarse eficazmente, la mejor opción es determinar cómo deshacerse de ellos mediante una nueva arquitectura. La figura 2 muestra una típica cadena de señales sin FI que consigue estos objetivos traduciendo la señal de RF directamente a una banda base compleja, eliminando por completo la necesidad de un filtro de FI y de amplificadores de FI. La selectividad se consigue introduciendo un par de filtros de paso bajo en la cadena de señal de banda base I/Q que pueden integrarse como filtros de paso bajo activos en lugar de dispositivos fijos de FI con pérdidas fuera del chip. Los filtros de FI SAW o LC tradicionales son de naturaleza fija, mientras que estos filtros activos se pueden sintonizar electrónicamente, a menudo en el rango de cientos de kHz a cientos de megahercios. Al cambiar el ancho de banda de la banda base, el mismo dispositivo puede cubrir una amplia gama de anchos de banda sin tener que cambiar de nomenclatura o pasar de un filtro de FI fijo a otro.

Aunque no se intuye en la figura, los receptores de FI cero también pueden cubrir una gama muy amplia de frecuencias de RF simplemente cambiando el oscilador local. Los transceptores Zero-IF ofrecen una verdadera experiencia de banda ancha con una cobertura continua típica de varios cientos de megahercios hasta unos 6 GHz. Sin filtros fijos, es posible contar con radios verdaderamente flexibles, lo que reduce en gran medida o elimina el esfuerzo necesario para desarrollar variaciones de banda del diseño de la radio. Con digitalizadores flexibles y filtros de banda base programables, los diseños cero-IF ofrecen no sólo un alto rendimiento, sino también la flexibilidad de adoptar una amplia gama de frecuencias y anchos de banda, manteniendo un rendimiento casi plano sin necesidad de optimizar los circuitos analógicos (como los filtros) para cada configuración: una verdadera tecnología de radio definida por software (SDR). También reduce significativamente la huella al eliminar los bancos de filtros para las aplicaciones que necesitan cubrir varias bandas. En algunos casos, el filtro de radiofrecuencia puede eliminarse por completo, lo que da lugar a una radio de banda ancha completa que no requiere prácticamente ningún esfuerzo para cambiar de banda. Al eliminar algunos dispositivos e integrar otros, la huella de la placa de circuito impreso necesaria para un diseño cero-IF se reduce enormemente, lo que no sólo simplifica el proceso de reagrupación, sino que también reduce el esfuerzo para cambiar el factor de forma cuando sea necesario.

La huella más pequeña

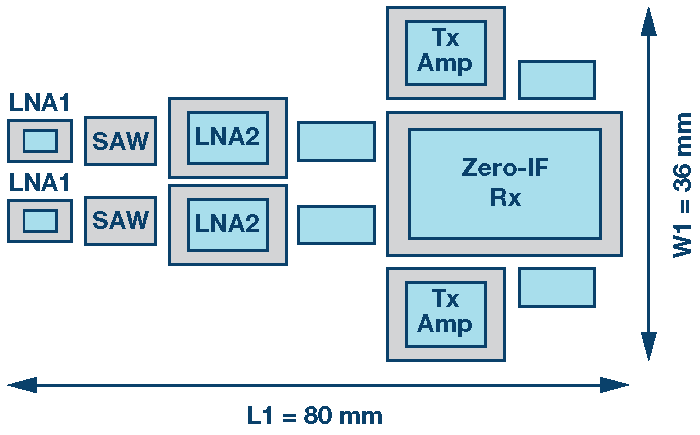

Una comparación directa del área de la placa de circuito impreso para cada una de estas arquitecturas (Figura 3 y Figura 4) muestra que para una ruta de recepción doble, el área respectiva de la placa de circuito impreso para una implementación razonable da 2880 mm2 (18 mm × 160 mm) para el muestreo IF y 1434 mm2 (18 mm × 80 mm) para el muestreo cero-IF. Por no hablar de la posible eliminación de los filtros de RF y otras simplificaciones,2 la arquitectura cero-IF tiene el potencial de reducir la huella de radio hasta un 50% en comparación con la tecnología actual de muestreo de IF. Los diseños de la futura generación pueden duplicar potencialmente este ahorro con una integración adicional.

El coste más bajo

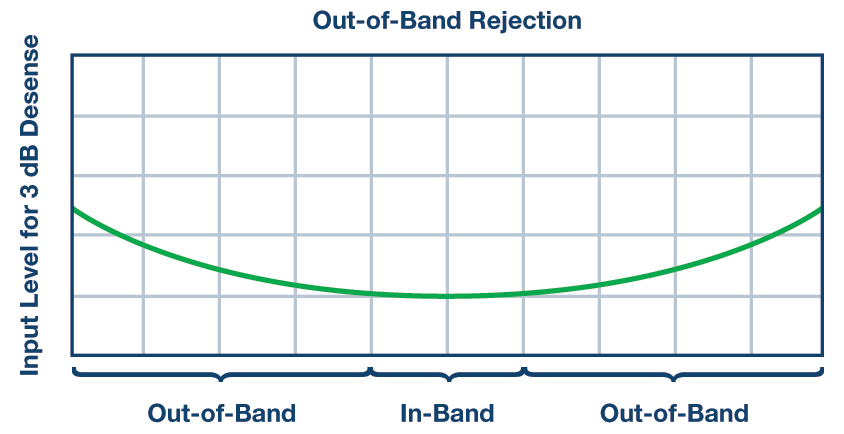

Desde la perspectiva directa de la lista de materiales, el ahorro que supone pasar de un sistema de muestreo de FI a una arquitectura de FI cero es del 33%. El análisis de costes siempre es difícil. Sin embargo, si observas detenidamente la Figura 1 y la Figura 2, verás que se han eliminado muchos componentes discretos, como el filtrado de FI y el antialiasing, y que el mezclador y los amplificadores de banda base están integrados. Lo que no es obvio es que, como los receptores de FI cero proporcionan intrínsecamente un rechazo fuera de banda que no está disponible en las arquitecturas tradicionales de muestreo de FI, los requisitos generales de filtrado externo se reducen considerablemente. A ello contribuyen dos elementos de la arquitectura del FI cero. El primero es el filtro activo de banda base, que proporciona tanto ganancia dentro de la banda como rechazo fuera de ella. El segundo es el convertidor de paso bajo Σ-Δ de alta frecuencia de muestreo que se utiliza para digitalizar las señales I/Q. El filtro activo reduce la componente fuera de banda, mientras que la alta frecuencia de muestreo del ADC desplaza el punto de alias a una frecuencia lo suficientemente alta como para que no sea necesario el filtrado antialiasing externo (porque el filtro activo ha rechazado suficientemente las señales).

Aplicando las señales de banda base a un filtro activo, como en la figura 5, se atenúa el contenido de alta frecuencia. A continuación, el ADC digitaliza y, por último, filtra cualquier salida residual del filtro de paso bajo. Los resultados en cascada se muestran en la Figura 6. Esta figura muestra cómo podría ser el rendimiento de un receptor típico con el efecto formado por un filtro activo y un ADC Σ-Δ. Aquí vemos una desensibilización típica de 3 dB de potencia dentro y fuera de banda. Observa la mejora en el rendimiento fuera de banda sin ningún filtro externo.

Para obtener niveles de rendimiento similares, los receptores de muestreo de FI dependen de un filtrado de FI discreto, como la tecnología SAW, para la selectividad y la protección contra las señales fuera de banda y para evitar el aliasing de las señales de banda ancha y el ruido que regresa a la banda. Las arquitecturas de muestreo de FI también tienen que estar protegidas de otros términos indeseables del mezclador, sobre todo el término de media FI, que conlleva requisitos adicionales de filtrado de RF e FI y limita las velocidades de muestreo y la planificación de la FI. La arquitectura cero-IF no tiene estas restricciones de planificación de frecuencias.

Según el diseño y la aplicación, este rechazo nativo reduce o elimina la necesidad de un filtrado de RF externo. Esto supone un ahorro de costes directo por su omisión, ya que los filtros de radiofrecuencia externos pueden ser relativamente caros según el tipo. En segundo lugar, la eliminación de estos dispositivos con pérdidas puede eliminar las etapas de ganancia de RF, lo que no sólo ahorra dinero, sino que también reduce la potencia y mejora la linealidad. Todo esto se suma al ahorro conseguido mediante la repartición y la integración inteligente.

Como se ha dicho, es difícil calcular el coste, ya que depende mucho del volumen y de los acuerdos con los proveedores. Sin embargo, un análisis detallado muestra que las arquitecturas cero-IF suelen reducir el coste total del sistema hasta en ⅓ gracias al impacto de la integración, la eliminación y la reducción de requisitos. Es importante recordar que se trata del coste del sistema, no del coste del aparato. A medida que se colocan más funciones en menos dispositivos, algunos costes de los dispositivos pueden aumentar mientras se reducen los costes generales del sistema.

Más allá de los costes de la lista de materiales, el receptor integrado cero-IF aborda otras áreas. Como los sistemas integrados reducen el número de dispositivos del sistema, los costes de montaje son menores y el rendimiento de la fábrica es mayor. Como hay menos dispositivos discretos, el tiempo de alineación es más corto. Juntos, estos elementos reducen los costes de la fábrica.

Como el receptor cero-IF es realmente de banda ancha, se reducen los costes de ingeniería para el reabastecimiento. Las frecuencias de FI deben elegirse cuidadosamente en los sistemas de muestreo de FI, pero con los sistemas de FI cero no se requiere una planificación cuidadosa. Se pueden añadir nuevas bandas en gran medida cambiando el oscilador local. Además, como muchas aplicaciones no requieren un filtro de RF externo cuando se utiliza el sistema de FI cero, se pueden conseguir más simplificaciones. En general, el ahorro puede ser sustancial cuando se considera una solución de FI cero si se tiene en cuenta el coste directo además de los costes de fabricación e ingeniería descritos anteriormente.

La potencia más baja

Tomar una arquitectura como la que se muestra en la Figura 1 e integrarla directamente en un sistema en chip no es suficiente para conseguir un ahorro de energía o de costes. El ahorro de energía proviene de la selección de una arquitectura eficiente que pueda ser optimizada para el proceso al que se dirige. Arquitecturas como el receptor de muestreo de FI presentado implican muchas frecuencias altas y medias que son difíciles de escalar a procesos de bajo coste y, por tanto, requieren grandes cantidades de disipación de energía para soportar las frecuencias requeridas. Sin embargo, la arquitectura cero-IF mostrada en la Figura 2 permite reducir inmediatamente las frecuencias de interés a cc (banda base), lo que permite implementar los circuitos de menor frecuencia posible.

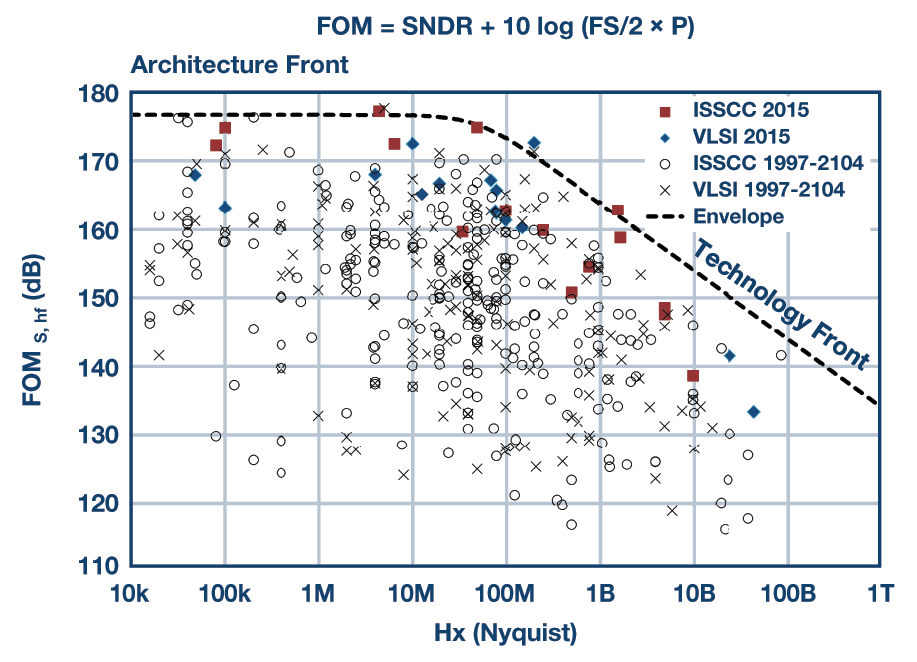

Del mismo modo, arrojar ancho de banda al problema también es ineficaz. Arquitecturas como el muestreo directo de RF ofrecen un gran ancho de banda con mucha flexibilidad. Sin embargo, añadir ancho de banda a un sistema siempre añade potencia extra al problema, como han demostrado los dos investigadores de Walden3 y Murmann.4

A menos que se necesite un ancho de banda bruto, abordar el problema sólo con el ancho de banda no es una solución económica para la mayoría de las aplicaciones de los receptores. Los datos de estos estudios a largo plazo muestran dos regiones de desarrollo del convertidor. El frente tecnológico documenta los avances tecnológicos que aumentan significativamente el rendimiento del núcleo del convertidor en términos de rango dinámico y ancho de banda. El frente de la arquitectura documenta los avances en la eficiencia general de la arquitectura del núcleo. En general, la curva se desplaza primero hacia la derecha y luego hacia arriba a medida que se optimizan los diseños. Para las aplicaciones de comunicación, el funcionamiento tiende a ser a lo largo del frente tecnológico, donde la pendiente de la línea es de unos 10 dB por década de reducción de la eficiencia del convertidor, como se muestra en la figura 7. Con esta pendiente, duplicar el ancho de banda equivale a disipar unas tres veces la potencia. Sin embargo, en el momento en que estos núcleos se integran en dispositivos funcionales, la eficiencia ha mejorado y, por lo general, conlleva una penalización de potencia más cercana a 2 a medida que se aproxima al frente arquitectónico.

La conclusión para las aplicaciones que se preocupan por la potencia es que la solución de menor potencia es aquella en la que el ancho de banda y la frecuencia de muestreo están optimizados para la aplicación. El muestreo de FI cero con convertidores Σ-Δ está optimizado para estas aplicaciones. Dependiendo de la implementación específica, el ahorro de energía al implementar un receptor de FI cero puede reducirse en un 50% o más en comparación con una arquitectura de muestreo de FI y hasta un 120% en comparación con el muestreo directo de RF.

La potencia también está directamente relacionada con el coste. No sólo una mayor potencia conlleva un embalaje y una generación de energía más caros, sino que por cada vatio que disipa un circuito, a 12 céntimos por kW/hora, el coste de funcionamiento es de más de un dólar al año por vatio. Dado el bajo coste de muchos aparatos electrónicos, la energía necesaria para hacerlos funcionar durante un solo año puede superar fácilmente su coste directo. Por lo tanto, a medida que se dispone de opciones de soluciones de radio integradas, las aplicaciones sensibles al coste y a la potencia deben elegir cuidadosamente las compensaciones. Elegir arquitecturas que aumenten innecesariamente la disipación no sólo puede aumentar la potencia, sino también repercutir en los costes de funcionamiento a largo plazo de la solución.

Mejora del rendimiento

Al diseñar una radio, hay una serie de medidas clave que se consideran importantes. Entre ellas se encuentran especificaciones como el factor de ruido (NF), la linealidad (IP3, IM3), la desensibilización y la selectividad, por nombrar sólo algunas. Más allá de las especificaciones normales de la radio, hay especificaciones adicionales que son importantes pero que suelen quedar ocultas para la mayoría de los usuarios. Se trata de la distribución y la deriva de las especificaciones en función del tiempo, la potencia, la temperatura y el proceso. Las arquitecturas Zero-IF abordan estos y otros requisitos clave del diseño de radio.

Temperatura, potencia y deriva del proceso

Una de las ventajas de una arquitectura de transceptor totalmente integrada es que la adaptación de los dispositivos puede ser mucho mejor para una radio correctamente diseñada, no sólo al principio, sino que los dispositivos pueden seguir eficazmente el proceso, la temperatura, la potencia y la frecuencia cuando se diseñan correctamente. Cualquier desajuste residual se elimina fácilmente mediante las técnicas de procesamiento de señales que suelen incorporar estas soluciones integradas. Aunque esto es muy típico del diseño de circuitos integrados, lo que es diferente en la integración de radio es que todos los elementos dependientes de la frecuencia están en el chip con un diseño libre de errores, y además pueden ser rastreados. Una radio típica, como se muestra en la Figura 1, incluye un filtro de FI fuera del chip. Las características del filtro de FI cambiarán con el tiempo, la temperatura o de un dispositivo a otro, lo que no se correlacionará con nada en el chip y no se podrá seguir. Sin embargo, una de las principales ventajas de integrar el filtro es que, al estar construido con dispositivos en el chip, éstos se pueden escalar o seguir racionalmente para mantener el rendimiento estable. Los elementos que no se pueden estabilizar por diseño se pueden calibrar fácilmente. El resultado final es que, al presupuestar las variaciones de los dispositivos, se necesita mucho menos margen que para un diseño discreto en el que todos los dispositivos no están correlacionados.

Por ejemplo, no es raro asignar una variación de NF de 1 dB para un mezclador, un filtro de FI, un amplificador de FI y un ADC cada uno. A la hora de presupuestar el rendimiento, estas variaciones deben ser en cascada. Sin embargo, en un diseño integrado en el que todas las especificaciones críticas se suceden o se calibran, el resultado es una variación de 1 dB para un solo dispositivo, lo que simplifica mucho la variación en la cadena de señales. Esto puede tener un impacto significativo en un diseño en comparación con un diseño con términos no correlacionados que, de otro modo, requeriría una ganancia adicional del sistema para compensar el posible aumento del coste, la potencia y la linealidad que afecta al ruido del producto final. En un diseño integrado como el que se muestra en la figura 2, la variación total del rendimiento es considerablemente menor que en un diseño no correlacionado y, por tanto, se requiere una menor ganancia del sistema.

Técnicas avanzadas de corrección

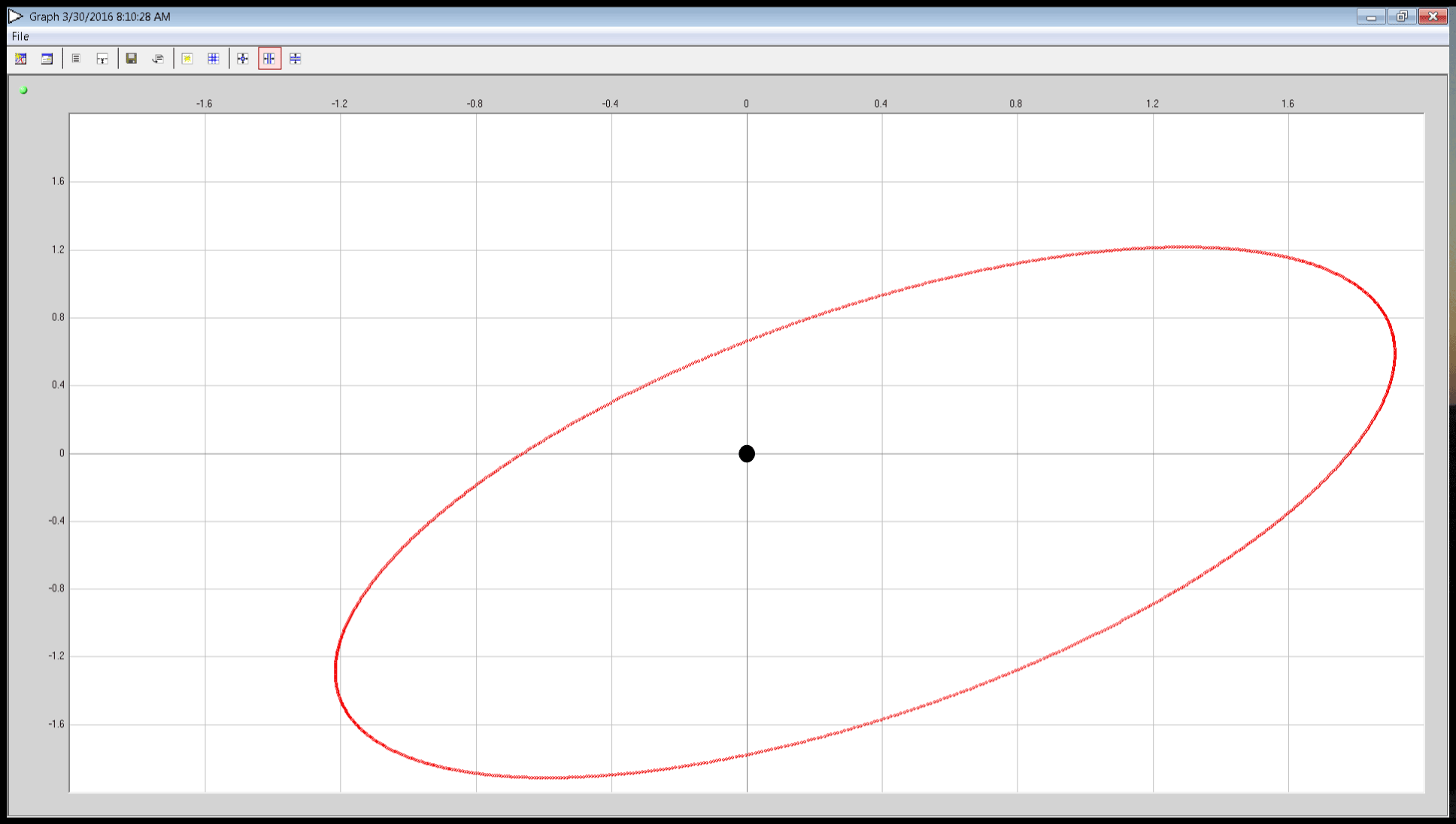

Los receptores cero-IF suelen tener dos aspectos que han sido motivo de preocupación en el pasado. Como los datos complejos se generan y se representan con un par de redes reales en cascada que representan los componentes reales e imaginarios, se generan errores que representan la ganancia, la fase y el desplazamiento de las cadenas de señales individuales, como se muestra en la figura 8.

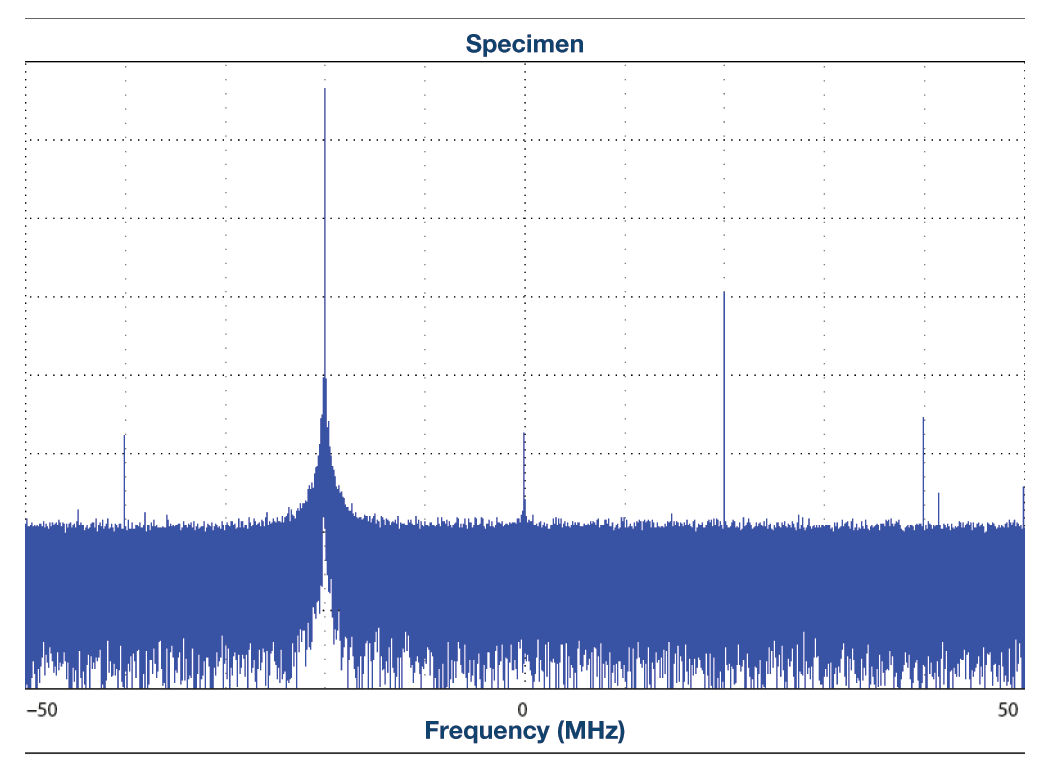

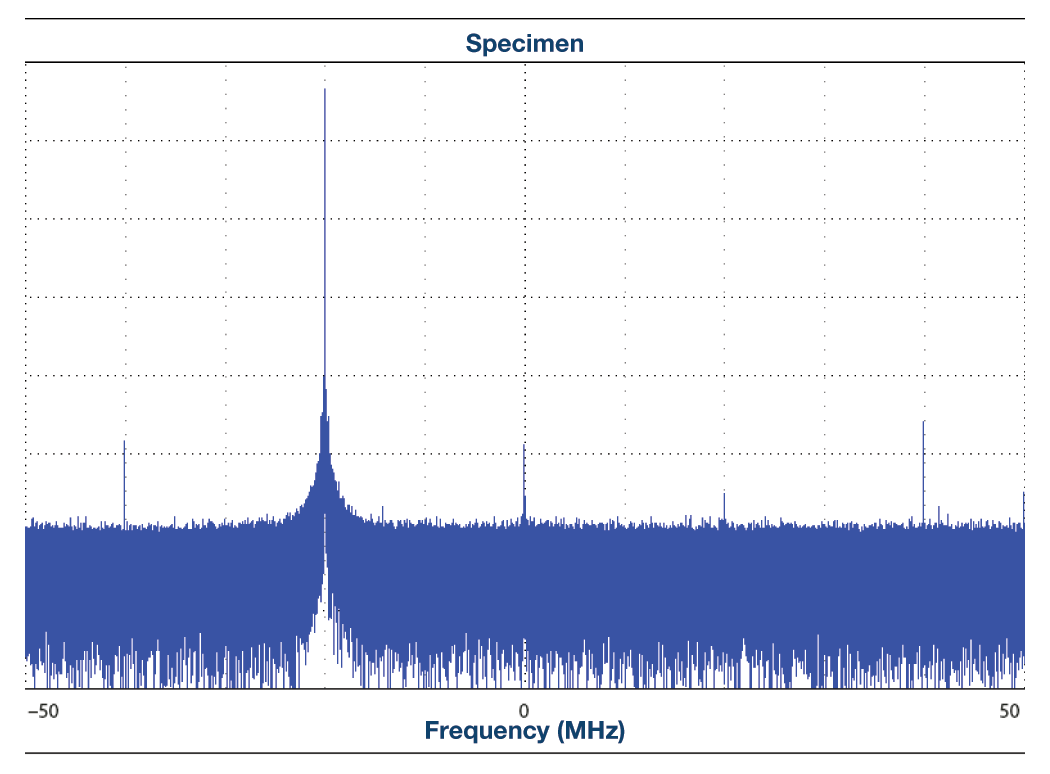

Estos errores se manifiestan en forma de imágenes en el espectro y son los que generalmente han impedido que estas arquitecturas se adopten más ampliamente. Sin embargo, como solución integrada, estos artefactos pueden controlarse fácilmente mediante la optimización analógica y la corrección digital. La figura 9 muestra una típica representación no corregida de datos complejos. Aquí podemos ver tanto la fuga de LO (y el desplazamiento de cc) como el rechazo de la imagen (error de cuadratura).

Control de fuga de LO

Las fugas de LO se manifiestan como un aumento del desplazamiento de CC en las rutas de la señal I o Q. Esto se produce como resultado del acoplamiento del LO directamente en la ruta de la señal de RF y la conversión coherente a la salida. El resultado es un producto de mezcla que aparece como un desplazamiento de CC, además de cualquier desplazamiento de CC residual en la cadena de señales. Una buena arquitectura de FI cero rastreará y corregirá automáticamente estos errores, tanto al principio como a medida que cambien con el tiempo, la temperatura, la fuente de alimentación y el proceso, lo que dará como resultado un rendimiento mejor que -90 dBFS, como se muestra en la Figura 10.

QEC

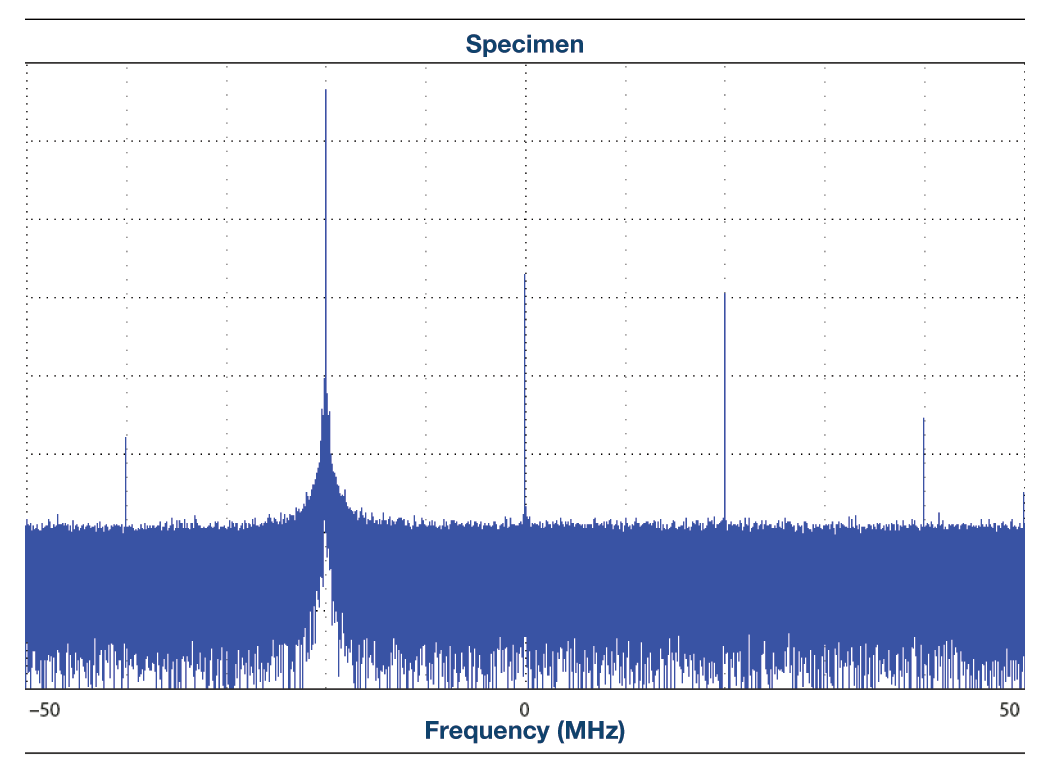

Para evitar que las imágenes interfieran en el rendimiento, suele aplicarse una corrección de errores en cuadratura (QEC). La figura 11 muestra el impacto que puede tener esa función. En este ejemplo, la imagen mejora a más de -105 dBc, lo que es más que adecuado para la mayoría de las aplicaciones inalámbricas. En el caso de la fuga de LO y la QEC, se utiliza el seguimiento para garantizar que, a medida que el rendimiento cambia con el tiempo, las correcciones se mantienen actualizadas, asegurando que siempre se consigue un rendimiento óptimo.

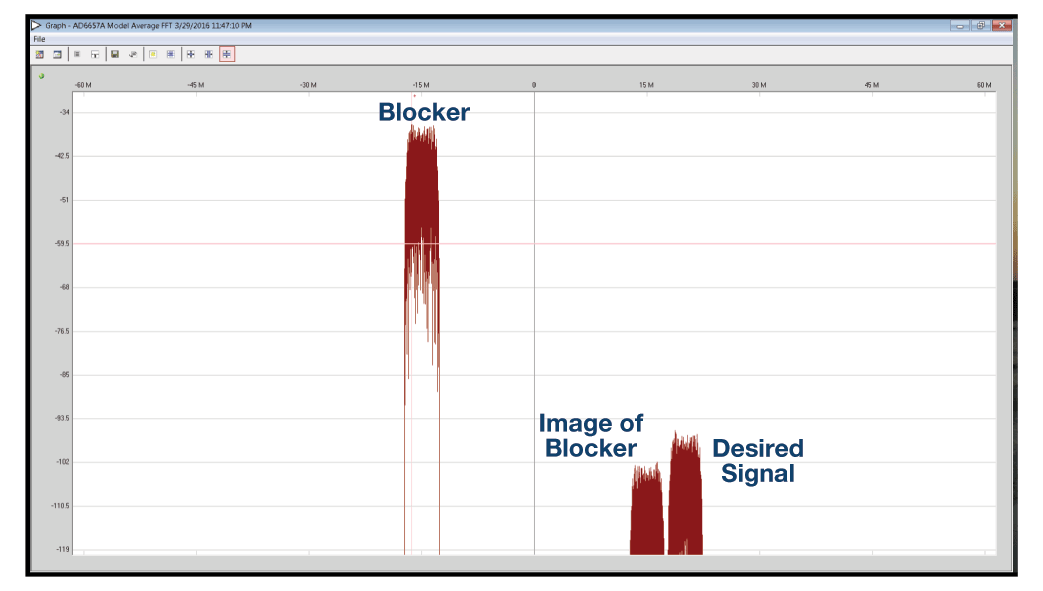

El error de cuadratura y la fuga de LO son importantes en un sistema de radio. Si el error es lo suficientemente grande, las imágenes de los bloqueadores grandes podrían enmascarar las señales deseadas más pequeñas. En la figura 12, la imagen de un gran bloqueador cae a 15 MHz, mientras que la señal deseada se centra en 20 MHz. Si una parte o la totalidad de la imagen hubiera caído sobre la señal deseada, habría degradado la SNR de la señal deseada, lo que podría provocar errores en la demodulación. En general, sistemas como LTE y W-CDMA tienen una tolerancia razonable a este tipo de imágenes, pero no son totalmente inmunes. En general, estos sistemas requieren un rechazo de la imagen de 75 dBc o superior, lo que, como se muestra en la figura 11, se consigue y mantiene fácilmente con una arquitectura de cero-IF.

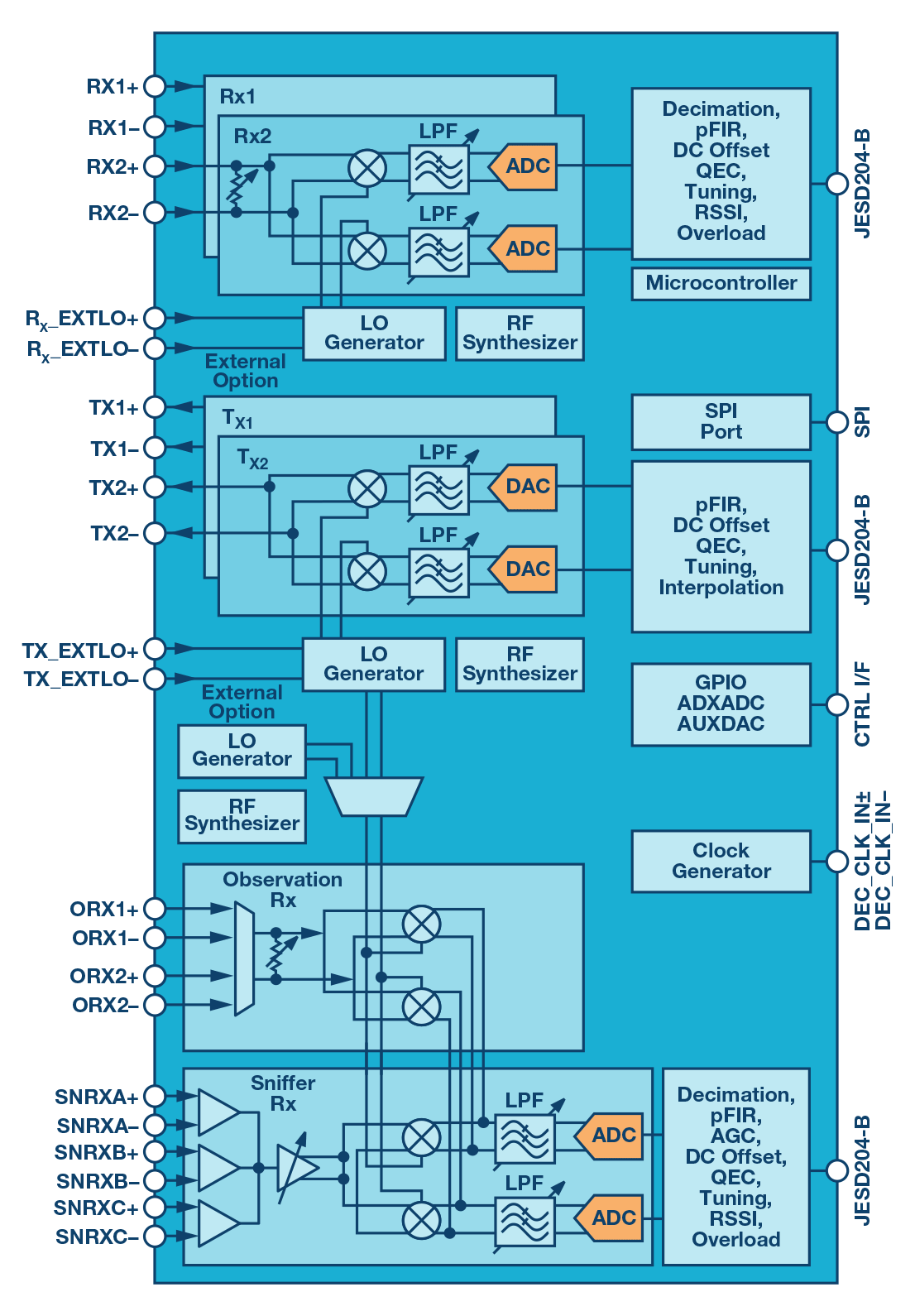

AD9371

El AD9371 es un ejemplo típico de transmisor y receptor de FI cero. Como se muestra en la Figura 13, el AD9371 ofrece un nivel muy alto de funcionalidad incorporada, incluyendo la transmisión y la recepción duales, así como características adicionales como un receptor de observación y un receptor de rastreo, así como AGC incorporado, corrección de desplazamiento de CC (control de fuga de LO) y QEC. El producto ofrece una amplia cobertura de RF de 300 MHz a 6 GHz. Cada transmisor puede cubrir entre 20 MHz y 100 MHz de ancho de banda de síntesis, mientras que cada receptor es capaz de cubrir entre 5 MHz y 100 MHz. Aunque este dispositivo está pensado para aplicaciones 3G y 4G, es una solución ideal para muchas otras radios de propósito general y aplicaciones definidas por software de hasta 6 GHz.

El AD9371 proporciona una integración completa del sistema, incluyendo todos los dispositivos dependientes de la frecuencia que hemos comentado anteriormente, así como toda la funcionalidad de calibración y alineación en un paquete BGA de 12 mm × 12 mm. Además de la funcionalidad de recepción de la figura 4, la figura 14 incluye la funcionalidad de transmisión necesaria en la huella para conseguir un diseño de transceptor doble muy compacto. La potencia depende de la configuración exacta, incluyendo el ancho de banda y las funciones habilitadas, pero la disipación típica del AD9371 es de sólo 4,86 W, incluyendo la funcionalidad digital para mantener la fuga de LO y el rechazo de la imagen.

Características principales del AD9371

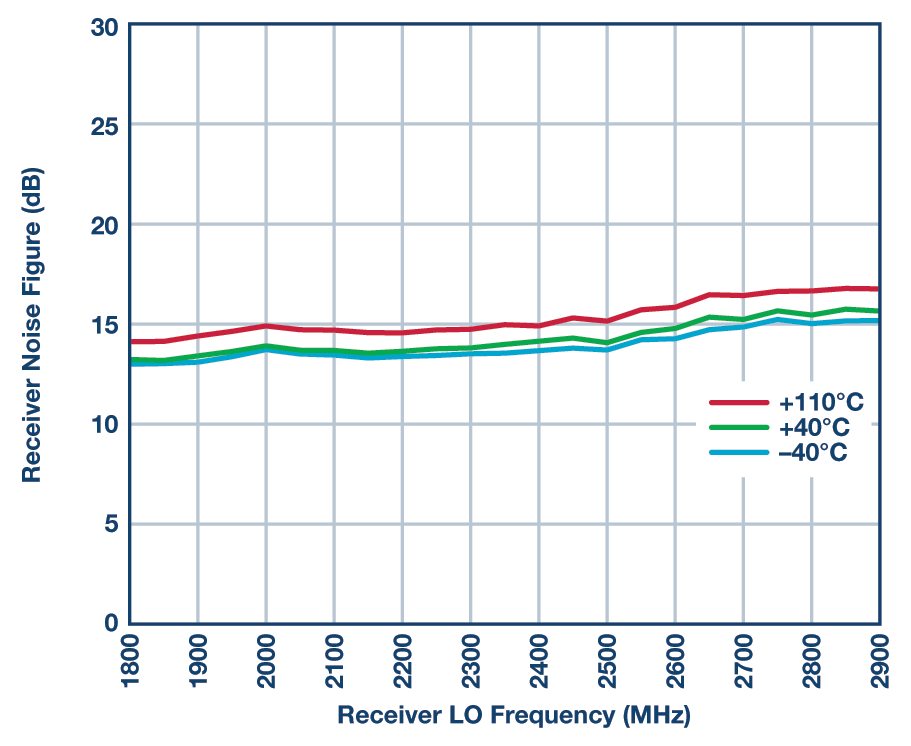

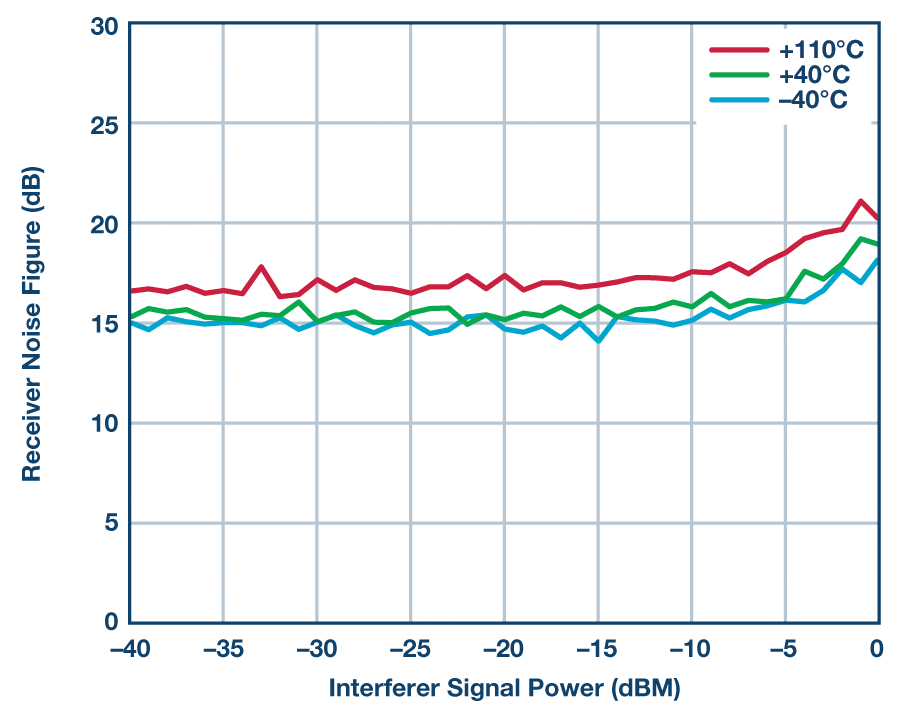

Cifra de ruido

La Figura 15 y la Figura 16 muestran las características típicas de NF del AD9371. La primera figura muestra un amplio barrido de la frecuencia de RF y que la NF es relativamente plana en este espectro. La estructura de entrada de este dispositivo tiene forma de atenuador, de modo que el NF aumenta dB por dB. Suponiendo una NF en el peor de los casos de 16 dB con atenuación cero, permitiendo una atenuación de unos 4 dB para las variaciones de ganancia externas, se puede suponer una NF total de 20 dB. Un LNA externo (0,8 dB) que proporcione una ganancia de al menos 24 dB daría un NF del sistema de 2 dB.

La figura 16 muestra la NF en función de los bloqueos fuera de banda respecto a la entrada del AD9371. Suponiendo una ganancia externa de 24 dB, 0 dBm respecto a la entrada de este dispositivo se produciría a -24 dBm respecto al conector de la antena. Considerando sólo el impacto del AD9371, la degradación global del NF sería de aproximadamente 1 dB para una degradación de 3 dB del receptor integrado.

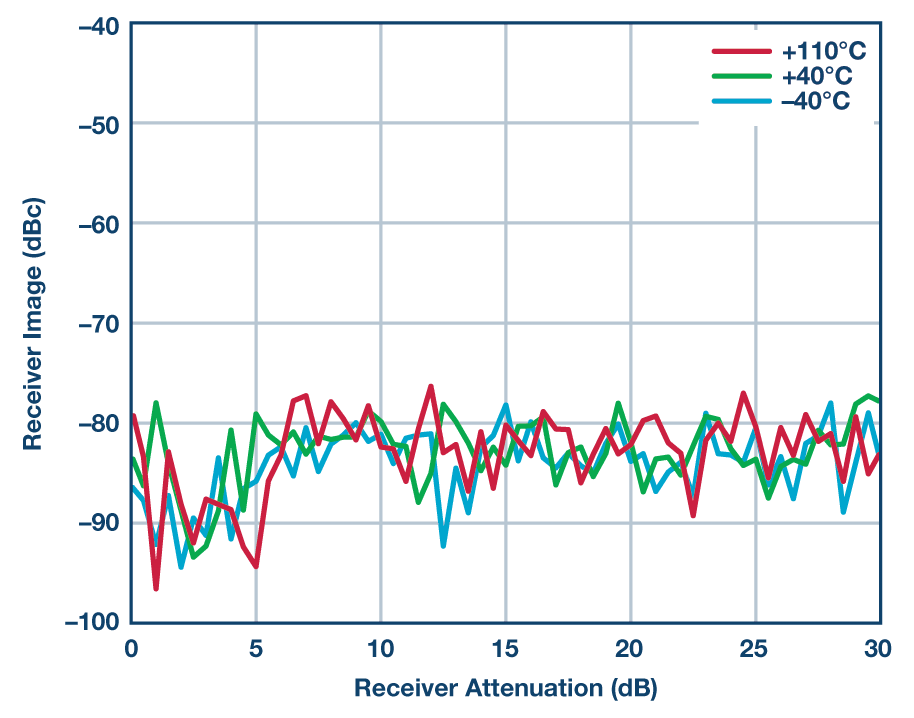

Rechazo de la imagen

Al igual que en el caso de la fuga de LO, el rechazo de la imagen de recepción puede estimarse mediante la información de la figura 17. Con un nivel de entrada típico en la antena de -40 dBm, la imagen puede estimarse a más de 80 dB o -120 dBm por debajo del puerto de la antena.

Conclusión

Mientras que, históricamente, las arquitecturas cero-IF se han limitado a aplicaciones de bajo rendimiento, los nuevos productos como el AD9371 ofrecen un rendimiento que cambia las reglas del juego. Estos dispositivos no sólo ofrecen un rendimiento en línea con los receptores de muestreo de FI, sino que van más allá al distribuir la radio para crear una arquitectura más robusta que no sólo reduce el coste de fabricación, sino también el coste de funcionamiento una vez desplegado. Ya no es necesario comprometer el rendimiento de la radio para conseguir un diseño de bajo coste, lo que permite a los usuarios dedicar tiempo y recursos al desarrollo de aplicaciones y no a la implementación de la radio.

Referencias

1Aunque esta discusión se centra en los receptores, también se aplica a los transmisores. Para los transmisores, la FI cero ha sido la arquitectura aceptada de alto rendimiento durante más de una década.

2Como se ha comentado aquí, el típico receptor Zero-IF también incluye una ruta de transmisión completa (AD9371) en la misma carcasa.

3R. H. Walden. "Estudio y análisis de los convertidores analógico-digitales" Revista del IEEE sobre áreas seleccionadas en comunicacionesabril de 1999.

4Boris Murmann. "Encuesta de rendimiento del CDA 1997-2015." Universidad de Stanford, 2015.

Si quieres conocer otros artículos parecidos a Donde gana Zero-IF: un 50% menos de huella de PCB a ⅓ del coste puedes visitar la categoría Generalidades.

Deja una respuesta

¡Más Contenido!