Una familia ADC compatible con entrada de pin alto facilita la conducción y amplía la selección de controladores ADC

Introducción

Las aplicaciones tales como equipos de prueba automatizados, automatización de máquinas, instrumentación industrial y médica requieren sistemas de adquisición de datos de precisión para analizar y digitalizar con precisión información física o analógica. Los diseñadores de sistemas que desean obtener las especificaciones completas de la hoja de datos de los ADC de aproximación sucesiva (SAR) precisa y de alta resolución a menudo se ven obligados a utilizar un amplificador de alta velocidad dedicado para controlar las entradas del ADC y los SAR tradicionales de condensador conmutado para sus aplicaciones de precisión. Este es uno de los problemas comunes que se encuentran al diseñar una cadena de señal de adquisición de datos de precisión, y este artículo presenta la familia de ADC AD4000 compatible con pines que resuelve este problema. Diseñado con tecnología ADI avanzada y arquitectura de vanguardia, esta familia de ADC SAR de precisión de 16/18/20 bits incorpora funciones fáciles de usar que brindan muchos beneficios a nivel de sistema que permiten una cadena de señal reducida. potencia y complejidad y mayor densidad de canales sin afectar significativamente el rendimiento. Una combinación única de modo Z alto, corriente de entrada baja junto con una etapa de adquisición larga facilita el desafío de la conducción ADC y reduce las demandas de estabilización en el controlador ADC. Esto amplía la elección de amplificadores para impulsar un ADC a amplificadores de precisión de baja potencia/bajo ancho de banda, incluidos JFET y amplificadores de instrumentación para aplicaciones de CC o de baja frecuencia (<10 kHz). Esta es una continuación de una versión publicada anteriormente. Diálogo analógico1 un artículo que presentará una amplia gama de amplificadores de precisión con un filtro RC de corte más bajo que puede controlar directamente este ADC y lograr el mejor rendimiento, eliminando una etapa de controlador ADC dedicada y ahorrando significativamente energía del sistema, espacio en la tarjeta y costo de BOM.

La entrada tradicional SAR ADC para conducir

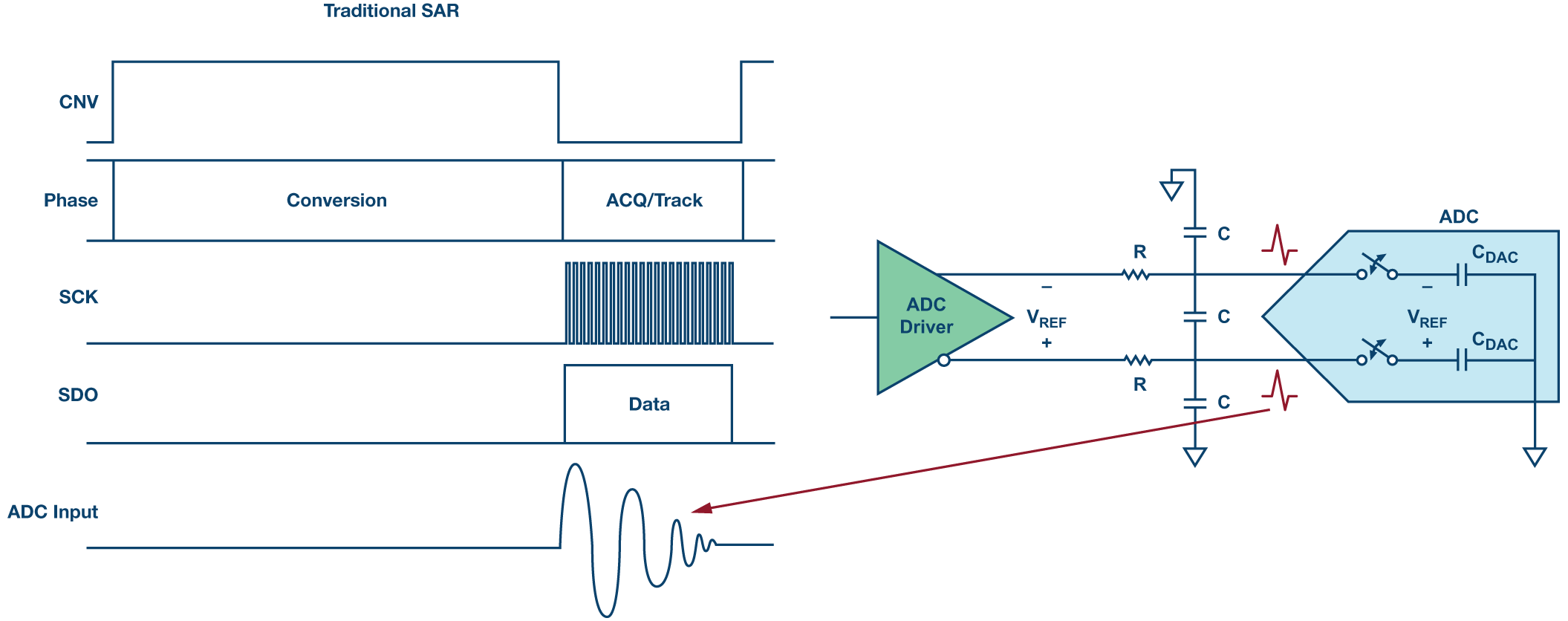

La Figura 1 muestra una cadena de señal típica utilizada en la construcción de sistemas de adquisición de datos de precisión. Tradicionalmente, la conducción de ADC SAR de alta resolución y precisión ha sido uno de los principales problemas y un problema complejo para los diseñadores de sistemas debido a la entrada de condensadores conmutados.

Los diseñadores de sistemas deben prestar mucha atención a la hoja de datos del controlador ADC y revisar las especificaciones de ruido, distorsión, margen de voltaje de entrada/salida, ancho de banda y tiempo de estabilización. Por lo general, se requieren controladores ADC de alta velocidad con gran ancho de banda, bajo ruido y alta potencia para ajustar el rebote del condensador de conmutación de las entradas SAR ADC dentro del tiempo de adquisición disponible. Esto reduce en gran medida las opciones disponibles para los amplificadores para impulsar el ADC y da como resultado compensaciones significativas de rendimiento/potencia/área. Además, la selección de un filtro RC apropiado para colocar entre el controlador y las entradas ADC impone restricciones adicionales en la selección y el rendimiento del amplificador. El filtro RC entre la salida del controlador ADC y la entrada SAR ADC es necesario para limitar el ruido de banda ancha y reducir los efectos del rebote de carga. Por lo general, el diseñador del sistema debe dedicar un tiempo considerable a evaluar la cadena de señal para asegurarse de que el controlador ADC y el filtro RC seleccionados puedan impulsar el ADC para lograr el rendimiento deseado.

Como se muestra en el diagrama de tiempo de la Figura 2, el rendimiento del ADC de SAR (1/tiempo de ciclo) incluye las etapas de conversión y adquisición, y los datos del ADC pueden sincronizarse mediante la interfaz serial SPI durante la etapa de adquisición. En la arquitectura SAR tradicional, la fase de conversión es generalmente más larga y la fase de adquisición es más corta. Durante la etapa de conversión, el capacitor ADC DAC se desconecta de las entradas ADC para realizar la conversión SAR. Las entradas se vuelven a conectar durante la etapa de adquisición y el controlador ADC debe configurar el rebote de entrada no lineal al voltaje correcto antes de que comience la siguiente etapa de conversión. El controlador ADC no puede ajustar el rebote de un ADC SAR tradicional dentro del tiempo de adquisición disponible con un filtrado agresivo que corta el ancho de banda RC inferior y, por lo tanto, se degrada el rendimiento de linealidad/distorsión del ADC.

Fase de adquisición más larga

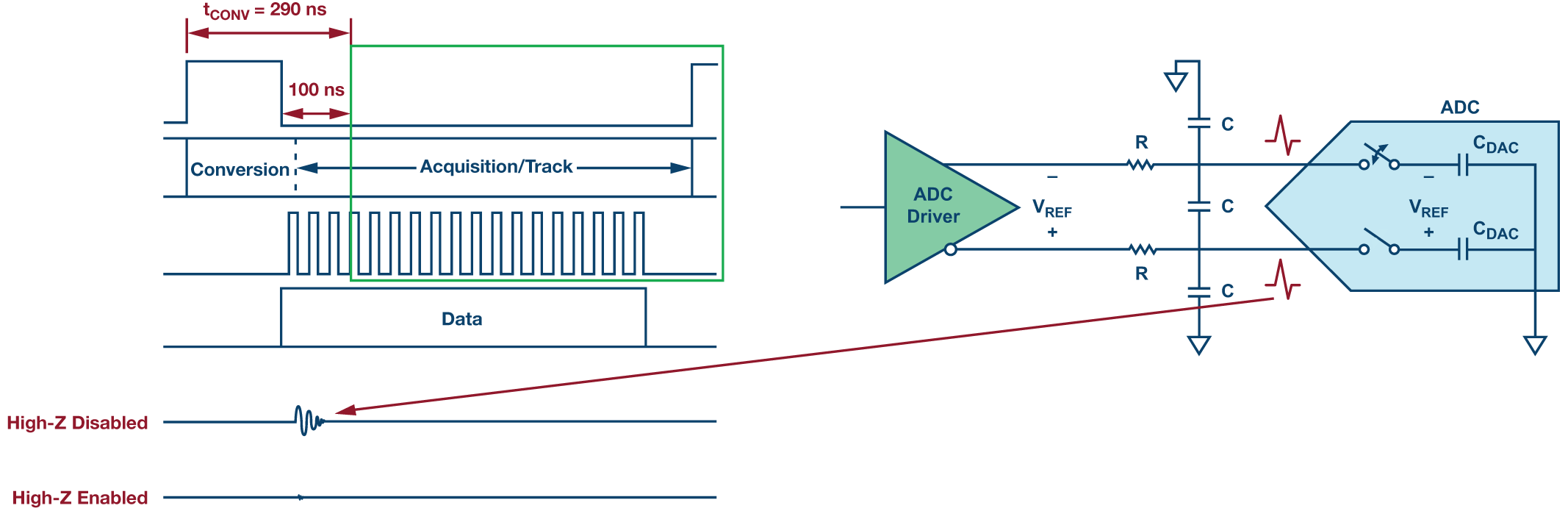

La familia AD4000 ADC tiene un tiempo de conversión muy rápido de 290 ns y el ADC vuelve a la etapa de adquisición 100 ns antes de que se complete el proceso de conversión actual, lo que permite una etapa de adquisición más larga, como se muestra en la Figura 3. La no linealidad de rebote vista desde este ADC reduce la entrada significativamente incluso cuando el modo de impedancia de entrada alta (Z) está deshabilitado y se reduce a niveles insignificantes cuando el modo Z alto está habilitado. Esto reduce la carga de tiempo de sintonización en el controlador ADC y permite un corte RC más bajo con una R grande, lo que significa que también se puede tolerar un ruido más alto y/o un amplificador de potencia/ancho de banda más bajo. Esto permite que el amplificador RC y el filtro frente al ADC se seleccionen en función del ancho de banda de la señal de interés y no en función de los requisitos de estabilización de las entradas de la tapa de conmutación. Se puede usar un valor mayor de R en el filtro RC con un valor menor correspondiente de C, lo que reduce los problemas de estabilidad del amplificador sin afectar significativamente el rendimiento de la distorsión. Un valor más alto de R ayuda a proteger las entradas del ADC de condiciones de sobrevoltaje y, como resultado, reduce la disipación de potencia dinámica en el amplificador. Otra ventaja de una etapa de adquisición más larga es que permite una velocidad de reloj SPI baja para reducir el consumo de energía de E/S, ampliar las alternativas para CPU/FPGA y simplificar los requisitos de diseño, el aislamiento digital sin afectar el rendimiento del ADC.

Método de alta Z

el es AD4000 La familia ADC incorpora un modo Z alto que reduce la retroalimentación de carga no lineal cuando el capacitor DAC regresa a la entrada al inicio de la adquisición. Cuando el modo Z alto está habilitado, el capacitor DAC se carga al final de la conversión para mantener el voltaje de muestreo anterior. Este proceso reduce cualquier efecto de carga no lineal del proceso de conversión que afecte el voltaje recibido en la entrada del ADC antes de la siguiente muestra. Las ventajas del modo High-Z son la eliminación de controladores ADC de alta velocidad dedicados y la expansión de la elección de amplificadores de precisión de baja potencia/bajo ancho de banda, incluidos JFET y amplificadores de instrumentación para señales de baja frecuencia (<10 kHz) o tipo CC.

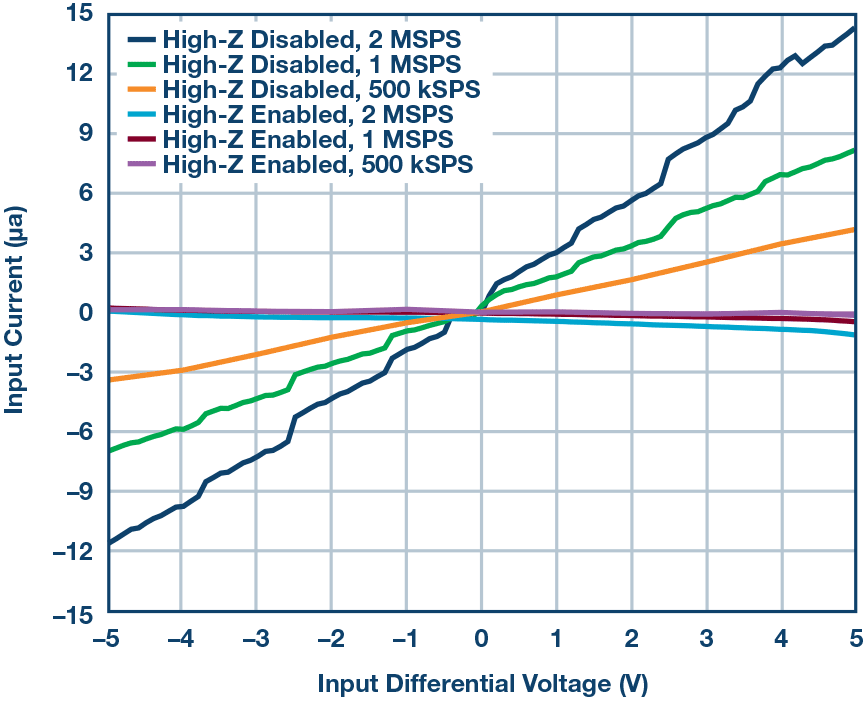

La Figura 4 muestra la corriente de entrada de AD4003/AD4007/AD4011 con el modo Z alto activado/desactivado. La baja corriente de entrada hace que el ADC sea mucho más fácil de manejar que los ADC SAR convencionales disponibles en el mercado, incluso con el modo Z alto desactivado. Si compara la corriente de entrada en la Figura 4 con el modo Z alto deshabilitado con el ADC AD7982 de la generación anterior, el AD4007 redujo la corriente de entrada en 4 × a 1 MSPS. La corriente de entrada se reduce aún más al rango de submicroamperios cuando el modo Z alto está habilitado.

Con la corriente de entrada reducida de esta familia de ADC, puede funcionar con una impedancia de fuente mucho más alta que los SAR convencionales. Esto significa que la resistencia en el filtro RC puede ser 10 veces mayor que en los diseños SAR tradicionales.

Los amplificadores de precisión impulsan directamente la familia AD4000 ADC

Para la mayoría de los sistemas, el front-end, no el propio CAN, generalmente limita el rendimiento general de CA/CC que puede lograr la cadena de señal. Se puede ver en la hoja de datos del amplificador de precisión seleccionado en la Figura 5 y la Figura 6 que su propio rendimiento de ruido y distorsión está por delante de las especificaciones de SNR y THD en una frecuencia de entrada dada. Sin embargo, esta familia de ADC de modo Z alto permite una selección mucho más amplia para amplificadores drivers, incluyendo amplificadores de precisión utilizados en etapas de acondicionamiento de señal, así como mayor flexibilidad en la selección de filtros RC y obtención del mejor rendimiento para el amplificador seleccionado.

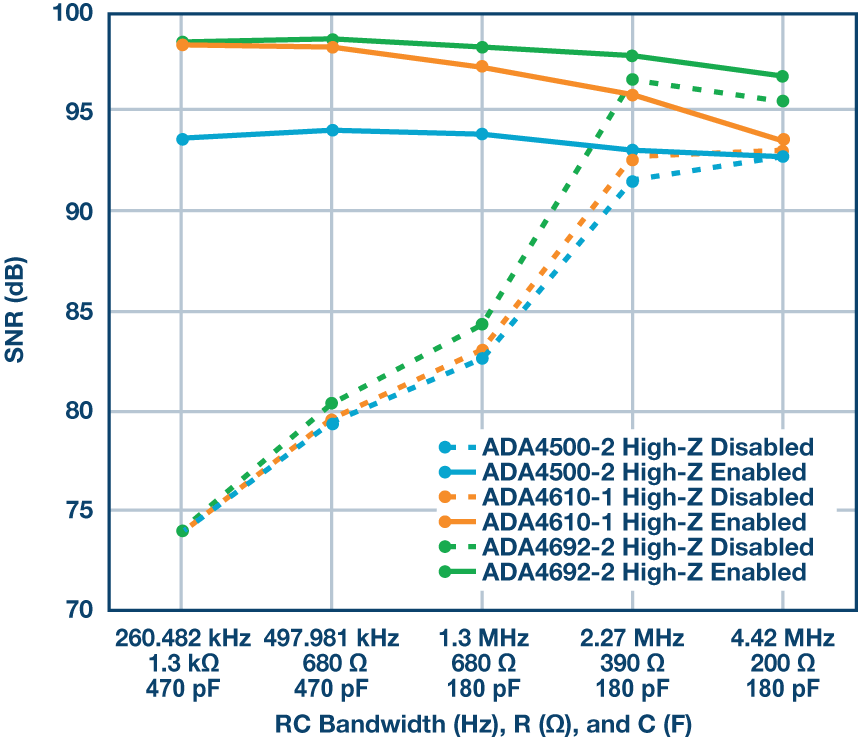

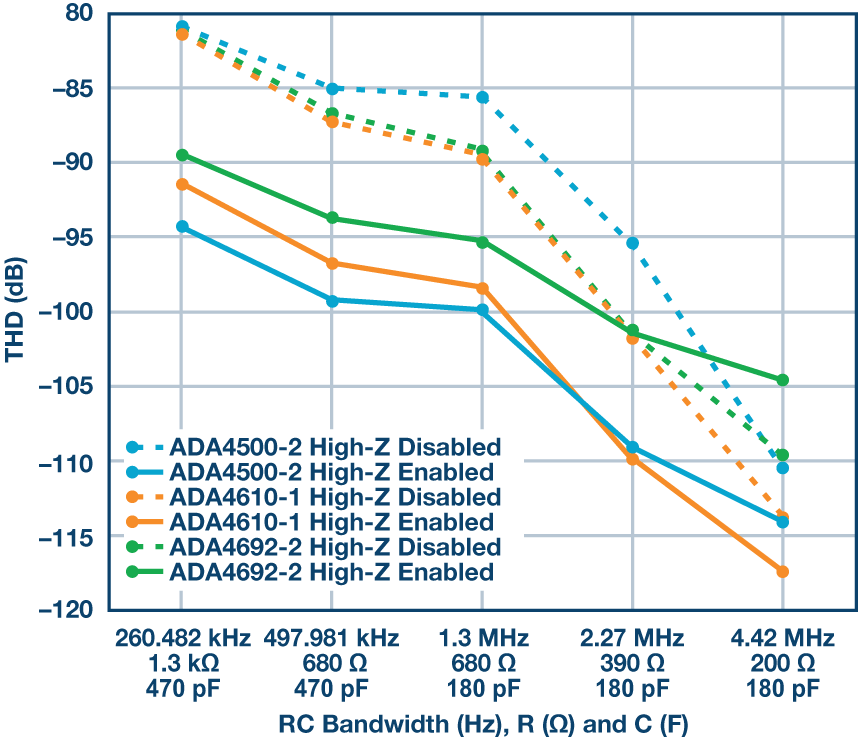

La Figura 5 y la Figura 6 muestran el rendimiento de SNR y THD del ADC AD4003/AD4020 usando el ADA4692-2 de bajo consumo (ICalma = 180 µA/amplificador), polarización de entrada baja JFET ADA4610-1 (ICalma = 1,5 mA/amplificador) y la distorsión de cruce por cero ADA4500-2 (ICalma = 1.55 mA/amplificador) amplificadores de precisión mientras maneja entradas ADC con un tono de entrada de 1 kHz usando una referencia de 5 V a velocidad completa para ambos casos con alta Z habilitada / deshabilitada con diferentes valores de filtro RC. Los amplificadores ADA4692-2 y ADA4610-1 logran una SNR típica superior a 98 dB con alta Z habilitada para anchos de banda RC más bajos de 260 kHz y 498 kHz, lo que ayuda a eliminar el ruido de banda ancha de los componentes en la cadena de señal aguas arriba cuando el ancho de banda de la señal de el interés es bajo. De acuerdo con los requisitos de la aplicación, los diseñadores pueden elegir un amplificador de precisión apropiado para controlar las entradas del ADC. Por ejemplo, el amplificador de riel a riel ADA4692-2, más adecuado para aplicaciones portátiles sensibles a la potencia, puede impulsar directamente este ADC de la familia y al mismo tiempo lograr el máximo rendimiento.

Con el modo High-Z habilitado, la SNR del AD4003/AD4020 es al menos 10 dB mayor incluso para anchos de banda RC por debajo de 1,3 MHz con valores R grandes por encima de 390 Ω y THD por encima de -104 dB en filtros RC de corte de 4,42 MHz que utilizan estos amplificadores Tenga en cuenta que esta familia de ADC se puede sobremuestrear utilizando la tasa de bits completa para lograr un mejor rendimiento de SNR con cortes de filtro RC más bajos.

Con High-Z habilitado, el AD4003/AD4020 generalmente consumirá de 2 mW/MSPS a 2,5 mW/MSPS de energía adicional, pero aún sería significativamente menor que usar controladores ADC dedicados como el ADA4807-1, y esta decisión genera ahorros en el área de PCB y BOM. Los diseñadores de sistemas pueden usar el controlador de menor potencia 5.5 × ADC ADA4692-2 (en comparación con el ADA4807), y este ADC aún logra un SinAD típico de aproximadamente 96 dB cuando el modo Z alto está deshabilitado para el ancho de banda de 2.27 MHz y 4.47 MHz BC. Cuando el modo de alta Z está habilitado, el rendimiento de ADC SNR/THD es mejor con controladores ADC, pero con el modo de alta Z deshabilitado, existe una compensación entre el rendimiento de ADC SNR/THD y los filtros RC discretos.

El amplificador de instrumentación impulsa directamente la familia AD4000 ADC

Los amplificadores de instrumentación brindan un excelente rendimiento de precisión, rechazo de modo común y alta impedancia de entrada para la interfaz directa con sensores, pero generalmente tienen un ancho de banda de señal ligeramente menor (<10 MHz). Los clientes que diseñan cadenas de señales de precisión (por ejemplo, ATE, equipos médicos) con ADC SAR y amplificadores de instrumentación suelen utilizar el acondicionamiento de señales o la etapa de controlador antes de enviar la señal a las entradas de ADC para el efecto de traducción y estabilización de nivel.

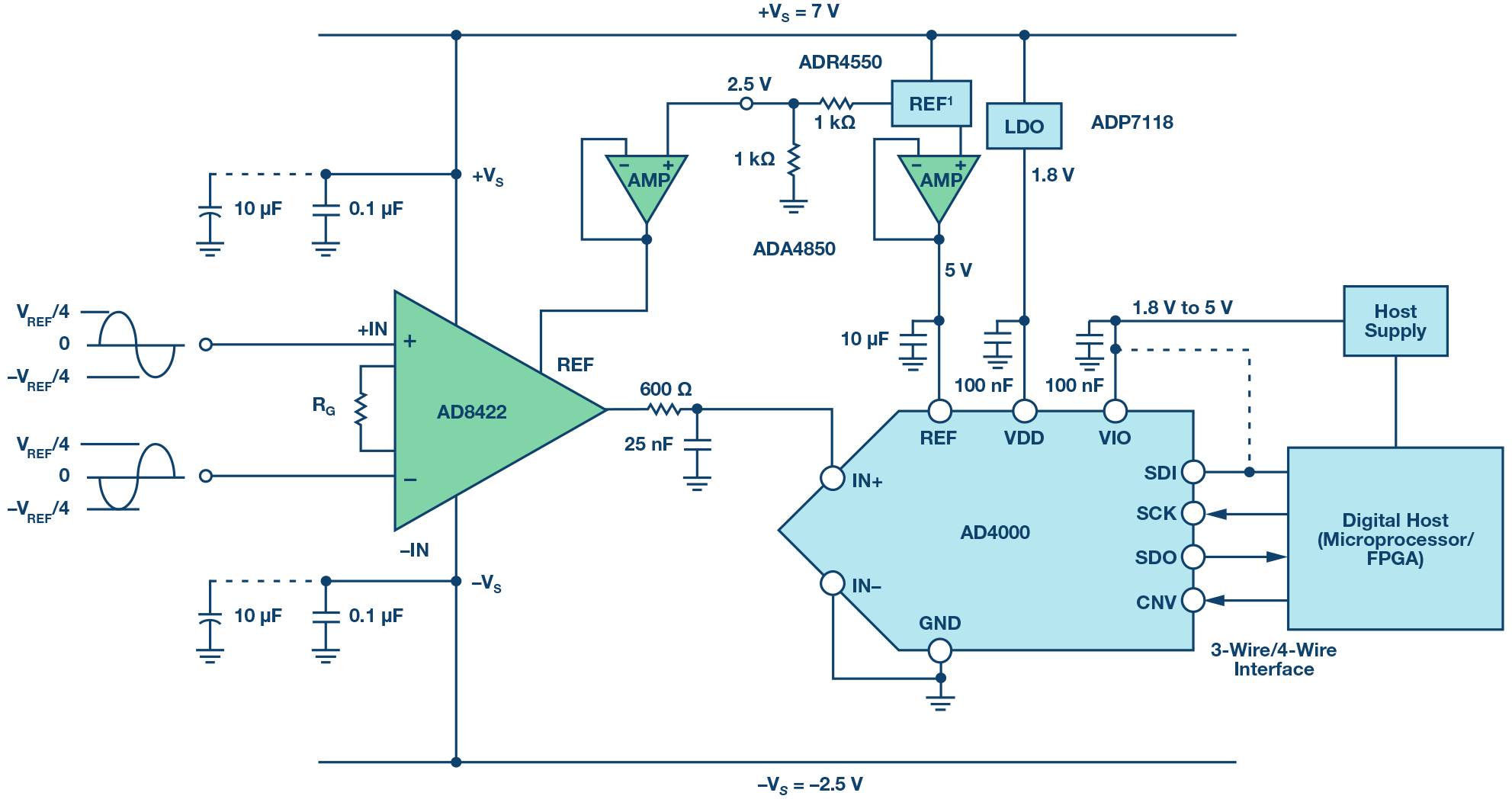

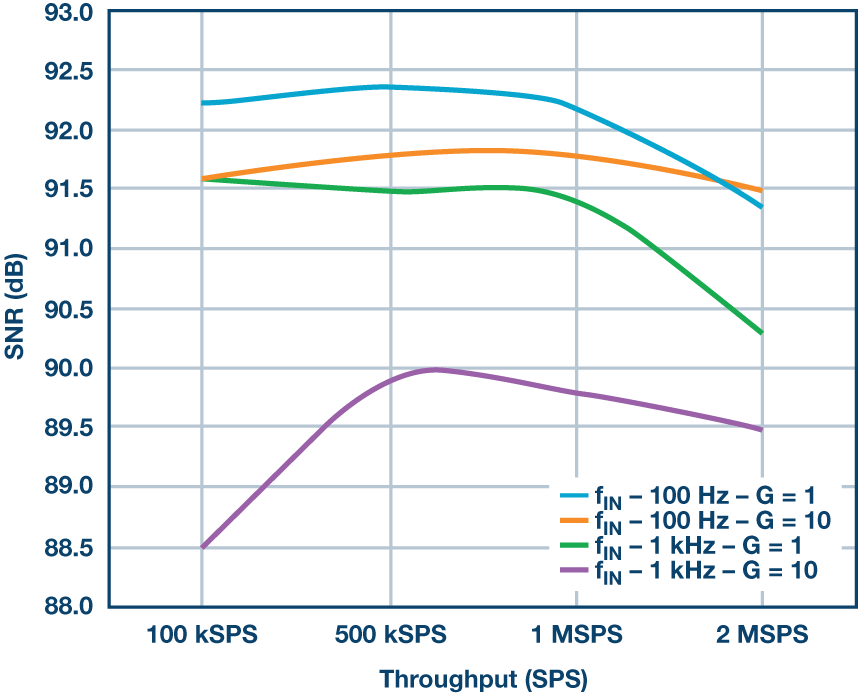

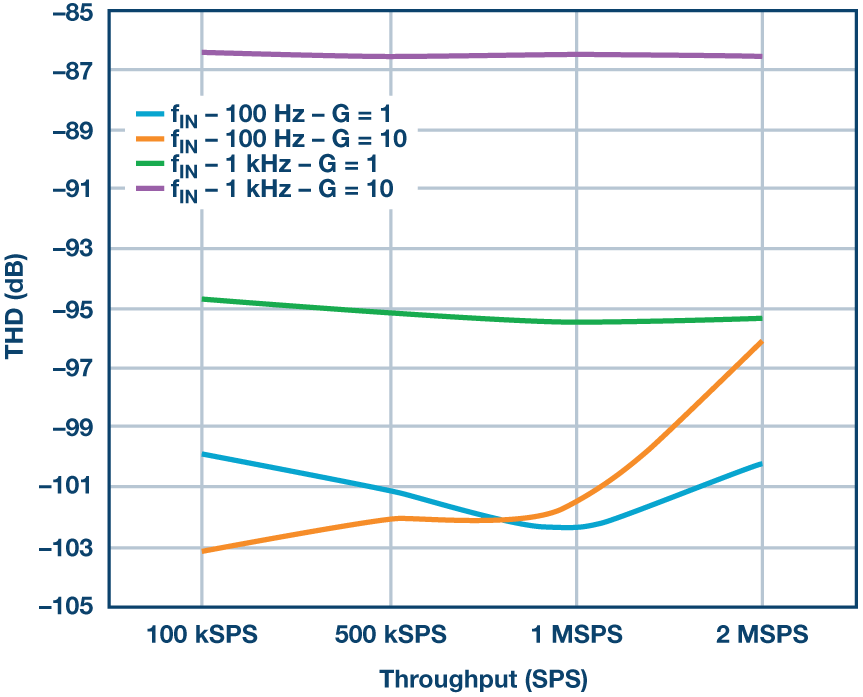

La Figura 7 muestra un diagrama de bloques simplificado del AD8422 que controla directamente el AD4000 cuando el modo Z alto está habilitado, lo que elimina la etapa del controlador y ahorra espacio en la placa. Los valores de filtro RC optimizados de 600 Ω y 25 nF se eligen en función del ancho de banda de interés para suprimir el ruido de banda ancha por encima de 10 kHz. El pin REF de AD8422 está polarizado en VÁRBITRO/2 y almacenado en búfer con ADA4805 para un rendimiento optimizado. Esta cadena de señal proporciona el mejor rendimiento de SNR y THD para una señal de entrada de 100 Hz y 1 kHz con una ganancia (definida por RG) de 1 (sin RG) y 10 (RG = 2,2 kΩ). La Figura 8 y la Figura 9 muestran que con la capacidad High-Z, el ADC logra más de 91 dB SNR y más de -96 dB THD para ganancias de 1 y 10 con una señal de entrada de 100 Hz para todos los rendimientos de hasta 2 MSPS. Como se muestra en la Figura 8 y la Figura 9, la SNR y la THD mejoran ligeramente a medida que se reduce el rendimiento del ADC, lo que proporciona un tiempo de adquisición más largo para ajustar el rebote de entrada.

Conclusión

La tabla 1 muestra la familia AD4000 de ADC SAR de 16/18/20 bits, de bajo consumo y compatible con clavijas, disponible en varias velocidades y tipos de entrada, que combinan funciones fáciles de usar y rendimiento de precisión, lo que permite a los diseñadores resolver problemas. . a nivel del sistema. desafíos técnicos.

| El rápido | 16 bits, desequilibrado | 16 bits, diferencial | 18 bits, desequilibrado | 18 bits, diferencial | 20 bits, diferencial |

| 2 SPSM | AD4000 | AD4001 | AD4002 | AD4003 | AD4020 |

| 1 SPSM | AD4004 | AD4005 | AD4006 | AD4007 | |

| 500kSPS | AD4008 | AD4010 | AD4011 |

La combinación única de la familia AD4000 ADC de modo Z alto, corriente de entrada más baja y etapa de adquisición más larga hace que la unidad sea más fácil y ayuda a los diseñadores a eliminar una etapa ADC de alta velocidad dedicada, lo que ahorra área de PCB, fuente de alimentación y costo de BOM y amplía su elección de ADC conductores Además, estas funciones permiten a los diseñadores optimizar los valores del filtro RC en función del ancho de banda de interés, mitigando problemas de ruido de banda ancha, estabilidad del amplificador, protección de entrada ADC y disipación de potencia dinámica. Este artículo demostró varios casos de uso para amplificadores de precisión, incluido un amplificador de instrumentación que controla directamente las entradas de esta familia ADC y cómo esta familia ayuda a resolver problemas comunes a nivel de sistema sin una interrupción importante en el rendimiento de precisión.

Referencias

1. Mathil Pachchigar y Alan Walsh. "El ADC SAR de próxima generación resuelve los puntos débiles en el diseño de la cadena de señal de adquisición de datos de precisión". Diálogo analógico, volar 50, diciembre de 2016.

Si quieres conocer otros artículos parecidos a Una familia ADC compatible con entrada de pin alto facilita la conducción y amplía la selección de controladores ADC puedes visitar la categoría Generalidades.

Deja una respuesta

¡Más Contenido!