Sincronice los relojes de muestra de una red de convertidores de datos

Los requisitos de mayor ancho de banda y soluciones de sistema en diversas aplicaciones, desde la infraestructura de comunicación hasta la instrumentación, aumentan la demanda de conexión de varios convertidores de datos de matriz. Los diseñadores necesitan encontrar una solución de bajo ruido y alta precisión para cronometrar y sincronizar una amplia variedad de convertidores de datos utilizando la popular interfaz de convertidor de datos en serie JESD204B.

Los dispositivos de generación de reloj con funciones de mitigación de jitter, VCO internos y múltiples salidas y muchas funciones de gestión de sincronización ahora están llegando al mercado para resolver este problema del sistema. Sin embargo, en muchas aplicaciones del mundo real, la cantidad de relojes necesarios en una red de conversión de datos excede lo que es posible con un solo componente IC. Los diseñadores a menudo recurren a la conexión de múltiples componentes de generación y distribución de relojes, creando un gran árbol de relojes.

Este artículo proporciona un estudio de caso real sobre cómo construir una red de extensión de reloj reprogramable y flexible que no solo mantenga un excelente rendimiento de ruido/fluctuación de fase, sino que también transmita la información de tiempo necesaria desde el primer dispositivo al reloj de árbol hasta el último con un control decisivo. . .

Introducción

La evolución de los sistemas de comunicación inalámbrica de 3G a 4G y LTE (y 5G, que actualmente se encuentra en discusión sobre especificaciones) ha sido un impulsor tecnológico clave para la conversión y sincronización de datos de alta velocidad. Hay una combinación de factores que aumentan el ancho de banda de datos requerido por las estaciones base celulares. Los principales impulsores son el crecimiento de suscriptores, la demanda de contenido multimedia más rico y nuevas aplicaciones en la comunicación de máquina a máquina utilizando la infraestructura celular global. Como resultado, los diseñadores están explorando arquitecturas de transceptores de RF nuevas e innovadoras con un mayor número de canales utilizando técnicas como el diseño de antena activa, MIMO masivo y formación de haces avanzada. Los sistemas con una gran cantidad de entradas y salidas utilizan múltiples rutas de transmisión y requieren una gran cantidad de componentes ADC y DAC. Dada la magnitud de los requisitos de conversión de datos, la generación y sincronización de relojes de muestra son importantes desafíos de diseño. En sistemas complejos, la cantidad de señales de reloj requeridas puede crecer fácilmente de unas pocas a cientos, como se muestra en la Figura 1.

Figura 1. Sistema de conversión de datos de árbol de reloj.

El estándar JESD204B define una interfaz de datos en serie, que se utiliza para reducir la cantidad de E/S de datos entre los convertidores de datos de banda ancha y otros circuitos integrados del sistema. Esta reducción en el tamaño de los datos de E/S resuelve el problema de interconectar convertidores de datos de alta velocidad y alto número de bits. La capacidad de ofrecer convertidores de datos de banda ancha con menos interconexiones simplifica el diseño de PCB y permite la implementación de un factor de forma más pequeño sin comprometer el rendimiento general del sistema. Estas mejoras son importantes para cumplir con el tamaño del sistema y las limitaciones de costos de la mayoría de las aplicaciones, incluida la infraestructura inalámbrica, la instrumentación portátil, las aplicaciones militares y los equipos médicos de ultrasonido.

Consideraciones a nivel del sistema

En sistemas complejos con grandes redes de convertidores de datos, un aumento en la cantidad de datos a procesar requiere un enlace SNR (relación señal a ruido) alto desde la antena a las unidades de procesamiento. Desde el punto de vista de la sincronización, la SNR está limitada por el ruido de fase del reloj de muestreo. El rendimiento deficiente del ruido de fase puede degradar el rendimiento del sistema al crear fluctuaciones y aumentar la EVM (magnitud del vector de error), lo que reduce significativamente la SNR. En general, la calidad de la señal de reloj se especifica en la fluctuación de fase, que se define como la integración del ruido de fase en un ancho de banda de interés definido. Los límites típicos de integración de ruido de fase son de 10 s kHz a 10 s MHz. Sin embargo, el ruido de banda ancha también es fundamental, ya que los pisos altos de ruido de la señal del reloj también afectarán la SNR del sistema. Un reloj de muestra deficiente también puede tener un contenido de señal espuria, lo que degradará el SFDR (rango dinámico libre de dispersión). Finalmente, la calidad del reloj de muestra debe definirse no solo en el dominio de la frecuencia, sino también en el dominio del tiempo, considerando parámetros como el ciclo de trabajo y el tiempo de subida/bajada.

Estos son los requisitos básicos del sistema para un reloj de muestra. Sin embargo, en grandes redes de convertidores de datos y cuando se requiere sincronización entre diferentes relojes de red, el desplazamiento entre canales se convierte en un requisito crítico. El rendimiento de estos sistemas depende de tablas de datos sincronizadas y, por lo tanto, es sensible a los retrasos entre diferentes convertidores de datos.

Otra consideración es el consumo de energía. Un mayor consumo de energía reduce la eficiencia del sistema, aumenta los costos de calefacción y refrigeración y puede conducir a mayores tasas de fallas. Desde un punto de vista comercial, el número de habitaciones y el espacio de la tarjeta también son importantes y deben controlarse.

Estructura del árbol del reloj

Como se mencionó, a menudo, en sistemas a gran escala, es posible que un IC de un solo reloj no tenga suficientes salidas para controlar todas las ramas. Una topología de árbol de reloj puede resolver este problema y poder sincronizar múltiples salas, dispositivos o múltiples sistemas. En la Figura 2 se muestra un diagrama de bloques de una topología de árbol de reloj. Tenga en cuenta que cada nivel del árbol introduce un componente de retardo, que consta de partes fijas y no deterministas.

Figura 2. Diagrama de bloques del árbol campana.

Los factores externos, como los cambios de voltaje y temperatura y las variaciones de proceso específicas del dispositivo, pueden afectar estos retrasos. Las imprecisiones aumentan, lo que lleva a variaciones de tiempo potencialmente inaceptables en los ADC y DAC, que deben sincronizarse a altas frecuencias simultáneamente. Debido a las altas frecuencias operativas requeridas en los sistemas actuales, se imponen estrictos tiempos de configuración y mantenimiento. Aunque los retrasos fijos pueden compensarse con un esfuerzo adicional, los retrasos indefinidos no pueden compensarse dentro del sistema. El objetivo de un diseñador, entonces, es minimizar o eliminar el elemento de retraso incierto controlándolo de alguna manera.

Además de estas limitaciones, el árbol debe ser flexible para que pueda aumentar el número de ramas y controlarlas fácilmente según las necesidades del sistema.

Un objetivo común al alinear los relojes y minimizar el sesgo del canal es realizar esta función de manera determinista, es decir, repetidamente para cada dispositivo y cada secuencia de encendido. En el sistema JESD204B, se requiere la alineación del reloj multitrama local (LMFC) para lograr una latencia determinista. La interfaz solicita el restablecimiento y la alineación de los LMFC en los dispositivos de transmisión y recepción, utilizando definiciones de subclase 1 (SYSREF) o subclase 2 (SYNC). Los retrasos inciertos en todo el sistema hacen que sea más difícil lograr la alineación de los LMFC durante el período LFMC. Por lo tanto, las estructuras de árbol de reloj mencionadas anteriormente ayudarían a los diseñadores de sistemas a lograr una alineación de alta precisión de los LMFC.

Además, los diseñadores deben asegurarse de que se cumplan los tiempos aceptables de configuración y espera para las señales SYSREF en relación con el reloj del dispositivo en todas las entradas del convertidor de datos. Si el diseño usa un solo chip, es un proceso simple para estimar los tiempos de configuración y espera para garantizar que se tengan en cuenta los márgenes de tiempo adecuados, pero, en las estructuras de árbol de reloj de múltiples dispositivos basadas en búferes de reloj simples, los tiempos de configuración y espera son más difíciles de controlar. . La estructura de árbol de reloj propuesta con sincronización determinista en múltiples capas ayuda a cumplir con los requisitos de configuración/mantenimiento de sincronización para cada par de reloj/dispositivo SYSREF en todas las capas. Esta estructura de árbol de reloj puede abordar las limitaciones de tiempo y alinear en fase los relojes de dispositivos de alta velocidad en cada convertidor de datos en diferentes capas.

Diseño de árbol de reloj

En la Figura 3 se muestra un ejemplo de un árbol de reloj de cuatro niveles, donde se utilizan un generador de reloj principal (HMC7044) y búferes de ventilador de tres niveles (HMC7043) para crear varios relojes de sincronización para los mapas. muestreo.

Figura 3. Ejemplo de un árbol de reloj con cuatro niveles.

HMC7044 se utiliza como raíz del árbol del reloj; Este es un generador de reloj de 14 salidas con mitigación de fluctuaciones que admite la temporización JESD204B. Los dispositivos HMC7043 (búferes de distribución ramificada de 14 salidas) se utilizan en todos los niveles de las sucursales. Estas partes son totalmente compatibles y su función de programación es muy similar, lo que facilita la combinación de partes y el aumento o disminución del nivel de distribución del reloj, lo que agrega flexibilidad al sistema.

La sincronización es posible entre todas las salidas en todos los niveles del árbol del reloj. En este sistema, las salidas del HMC7044 se pueden alinear progresivamente con comandos SPI o con mayor precisión utilizando un pulso SYNC. El comando restablece el temporizador HMC7044 SYSREF común, que controla los divisores de salida para cada reloj. Todos los divisores de reloj de salida se alinean simultáneamente con los comandos del temporizador SYSREF. El retraso entre el comando SYNC y el temporizador SYSREF y el retraso entre los tiempos de encendido y apagado están bien definidos, lo que permite la sincronización y un retraso determinista entre las salidas. Además, cualquier salida se puede programar para generar un número determinado de pulsos para usar como pulsos SYSREF en el sistema.

La parte de distribución del reloj, HMC7043, también incluye una estructura de temporizador SYSREF muy similar. El dispositivo utiliza la señal RFSINC para la alineación. Un pulso RFSYNC iniciará el mismo proceso que una señal SYNC del HMC7044, y todas las salidas se sincronizarán con alta precisión. Nuevamente, las salidas se pueden configurar en modo de pulso para usarlas como pulsos SYSREF.

La estructura de árbol de reloj propuesta utiliza esencialmente las señales SYSREF como la señal RFSYNC al HMC7043 para el siguiente nivel y mantiene la alineación de fase en las salidas en cada nivel. A través de un cuidadoso diseño arquitectónico, todas estas señales de temporización son definitivas y proporcionan un estricto control de asimetría. Además, cada sección incluye una estructura de retardo analógico para que cualquier diferencia en el sesgo entre las salidas o la irregularidad en la longitud de la línea se pueda compensar en la fuente.

Para las redes complejas de convertidores de datos que se utilizan en los sistemas de RF, es posible que se requieran diferentes frecuencias porque los ADC, DAC, FPGA, los osciladores locales y los mezcladores pueden sincronizarse a diferentes frecuencias. El HMC7044 y el HMC7043 tienen divisores incorporados que permiten generar múltiples frecuencias. Además, el HMC7044 tiene una estructura PLL dual con un VCO incorporado que permite la generación de relojes de alta frecuencia sin componentes adicionales.

Una complicación adicional en los sistemas de comunicación comunes es que la mayoría de los front-end de RF se basan en interfaces seriales para los bloques de transmisión/recepción, que requieren que los datos y el reloj sean integrados/desintegrados por un procesador digital o FPGA. Este proceso a menudo produce fluctuaciones de reloj de referencia no deseadas y requiere la inclusión de la capacidad de mitigación de fluctuaciones en dispositivos grandes de generación y distribución de relojes de RF, como el HMC7044.

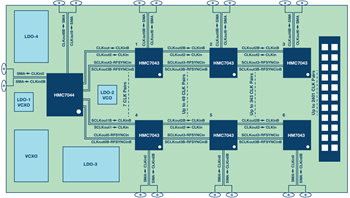

La figura 4 muestra la solución compacta que se puede utilizar en matrices de convertidores de datos.

Figura 4. Solución compacta del árbol de reloj de cuatro niveles.

Resultados de la prueba

En la Figura 5, se muestra el desplazamiento entre todas las salidas. Las señales amarillas y remotas son pulsos SYSREF y señales de reloj continuas para los 4mi salida de nivel, que se sincroniza sin ajustes de retardo adicionales. La señal de la línea azul es la señal SYSREF continua del HMC7044 y, mediante el uso de la función de retardo analógico, se sincroniza con los 4mi nivel de salida. En este ejemplo, se obtiene un sesgo total de menos de 16 ps.

Figura 5. Respuesta en el dominio del tiempo de la salida de cuatro niveles.

El rendimiento de ruido de fase del árbol de reloj de cuatro niveles se puede ver en la Figura 6. El ruido de fase del generador de reloj también se muestra con la línea azul más clara. No hay degradación hasta un cambio de 2 MHz en el ruido de fase total. Debido al ruido aditivo (jitter aditivo) de cada nivel, la degradación del ruido de fondo es inevitable y se puede ver en el gráfico con el aumento de ruido de 6 dB en esta sección. El HMC7044 y el HMC7043 tienen el mismo nivel de ruido de salida (alrededor de –154 dBc/Hz) y el ruido de las cuatro partes se degrada a -148 dBc/Hz, que sigue siendo un nivel aceptable para la mayoría de los sistemas.

Figura 6. Respuesta en el dominio de la frecuencia de una salida de cuatro niveles.

El ruido incorporado se calcula de 12 kHz a 20 MHz a 2457,6 MHz a 52,7 fs rms Jitter, solo unos pocos fs rms degradados de la salida HMC7044. En casi todos los sistemas prácticos, esta degradación es tolerable, sin embargo, si no es aceptable, el HMC7043 se puede reemplazar con el HMC7043, que mitiga cualquier fluctuación acumulada en el mismo árbol del reloj.

Como se mencionó, en los sistemas donde se utilizan una gran cantidad de convertidores de datos, el consumo de energía se convierte en uno de los temas más importantes. Un factor crítico en el consumo de energía de un árbol de reloj de este tipo es el tipo de señalización utilizada. Los modos de señalización de salida del HMC7044 y el HMC7043 se pueden cambiar a través del control del software de forma independiente entre sí, lo que brinda la capacidad de intercambiar el consumo de energía y la potencia de accionamiento en función de la frecuencia. Una pauta general es que LVDS se puede usar con bajo consumo de energía a bajas frecuencias y, a altas frecuencias, LVPECL y CML brindan el mejor rendimiento.

Conclusión

La discusión en este artículo cubre muchos sistemas diferentes que utilizan grandes redes de convertidores de datos distribuidos, desde infraestructura inalámbrica hasta radares militares y sistemas de prueba y medición. Los esquemas de modulación de ancho de banda de frecuencia más alta que se ofrecen en los sistemas de comunicación 5G recientes se basan en las tendencias actuales de múltiples interfaces de entrada/salida de RF, que requieren una mayor cantidad de rutas de comunicación. Además, en algunas de las propuestas recientes de arquitectura 5G, las antenas de matriz en fase se analizan ampliamente como una forma de ahorrar energía y aumentar la capacidad de salida.

Ampliamente desplegadas en los sistemas de comunicaciones militares, las técnicas de matriz en fase no solo requieren una gran cantidad de relojes, sino también una sincronización precisa de esos relojes.

Otro caso de uso importante para las grandes matrices de conversión de datos son los sistemas de prueba y medición, en los que es necesario capturar grandes cantidades de datos a altas tasas de muestreo, agregando el menor ruido posible y procesando simultáneamente. Estos sistemas también requieren una gran cantidad de relojes sincronizados. De manera similar, con los sistemas avanzados de imágenes médicas, las tasas de rendimiento de datos son altas y requieren una operación sincrónica de los canales de adquisición de datos simultáneos.

Como se muestra aquí, las empresas de circuitos integrados brindan soluciones creativas y prácticas para implementar estos diseños avanzados. Los componentes como el HMC7044 y el HMC7043 se desarrollan teniendo en cuenta los desafíos del sistema y tienen como objetivo crear árboles de reloj flexibles y de alto rendimiento, al tiempo que mantienen la precisión de fase determinista en múltiples niveles de extensión de datos.

Si quieres conocer otros artículos parecidos a Sincronice los relojes de muestra de una red de convertidores de datos puedes visitar la categoría Generalidades.

Deja una respuesta

¡Más Contenido!