Introducción al escalado dinámico de potencia

En los sistemas de adquisición de datos (DAQ) actuales, los límites de rendimiento se superan continuamente. Los diseñadores de sistemas requieren mayor velocidad, menor ruido y mejor rendimiento de distorsión armónica total (THD), todo lo cual es posible pero ninguno es gratuito. Estas mejoras de rendimiento generalmente tienen el costo de corrientes operativas más altas, lo que a su vez resulta en una mayor disipación de energía. Sin embargo, en muchas aplicaciones, la sensibilidad al consumo de energía también es una preocupación cada vez mayor. Las razones son variadas. Puede ser un sistema remoto que opere desde una batería de tipo botón donde la preocupación principal es la vida útil de la batería, o quizás un sistema multicanal donde la concentración de calor de un alto número de canales y una alta densidad de circuitos pueden sumarse a problemas de deriva inducidos por la temperatura. En cualquier caso, minimizar el consumo de corriente y la disipación de energía es de suma importancia. El diseñador del sistema debe lograr un equilibrio entre las prioridades contrapuestas de mayor rendimiento y menor consumo de energía. Un camino hacia una solución es a través de un proceso llamado escalado dinámico de potencia (DPS).

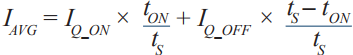

En pocas palabras, DPS es el proceso de habilitar dinámicamente un componente electrónico cuando es necesario y deshabilitarlo cuando no lo es. La figura 1 muestra un subsistema típico de adquisición de datos basado en ADC de SAR. Uno de los atributos clave del SAR ADC es que su potencia escala con la tasa de rendimiento, lo que lo convierte en una opción muy atractiva para aplicaciones sensibles a la potencia. Históricamente, el controlador ADC y el búfer de referencia no han compartido la escala de potencia automática que disfruta el SAR. Por lo general, se encienden y habilitan cada vez que el sistema está funcionando, por lo que consumen un exceso de energía. Suponiendo un tiempo de habilitación lo suficientemente rápido, el pin de apagado del amplificador puede activarse dinámicamente para deshabilitar el amplificador entre conversiones de ADC. Esta es la escala de potencia dinámica. Al aplicar DPS al amplificador, su consumo de corriente promedio se puede reducir considerablemente. Con DPS, la corriente de reposo del amplificador es una función del ciclo de trabajo en el que se acciona el pin de apagado. La corriente de reposo promedio teórica está dada por

Dónde:

- yoPROMEDIO es la corriente de reposo DPS promedio

- yoQ_ON ¿Está habilitada la corriente de reposo del amplificador?

- yoQ_APAGADO ¿Está desactivada la corriente de reposo del amplificador?

- tEN es el tiempo que el amplificador está habilitado

- tS es el período de frecuencia de muestreo

Figura 1. Diagrama de bloques del subsistema de adquisición de datos basado en SAR ADC.

En el resto de este artículo, el amplificador del controlador ADC será el punto focal, pero los conceptos de DPS también se pueden aplicar al búfer de referencia con resultados similares.

La Figura 2 muestra las mejoras de eficiencia teóricas del amplificador del controlador ADC cuando está constantemente habilitado. La línea de referencia vertical en fR representa la frecuencia de muestreo en la que el consumo de energía del ADC es igual al del amplificador del controlador constantemente habilitado. A frecuencias de muestreo más bajas, el amplificador domina el consumo de energía y a frecuencias de muestreo más altas domina el ADC. La frecuencia de referencia (fR) variará según el consumo de energía del amplificador y el ADC elegido, pero los conceptos básicos siguen siendo los mismos. Las mejoras de eficiencia relativa para el mismo amplificador escalado en potencia se muestran para tres valores diferentes de tEN. Como era de esperar, un t más cortoEN da como resultado una mayor eficiencia a una frecuencia de muestreo dada y permite el uso de DPS a frecuencias de muestreo más altas. La región sombreada muestra que el área de mayor mejora para el acortamiento incremental de tEN generalmente se extiende hasta aproximadamente una década por debajo de fR. A medida que la frecuencia de muestreo continúa disminuyendo por debajo de ese punto, se obtienen los mayores ahorros de energía en general, pero se obtiene el beneficio adicional de acortar aún más el t.EN es insignificante ya que el consumo de energía se acerca asintóticamente al del estado de apagado o deshabilitado.

Figura 2. Consumo teórico de potencia del amplificador para DPS en el t seleccionadoEN (relativo al amplificador constantemente habilitado).

Para lograr un rendimiento óptimo con DPS, el sistema de temporización y determinación del t mínimoEN son críticos.

La Figura 3 muestra un diagrama de tiempo simplificado para el ADC y el amplificador del controlador. El bloque de temporización del sistema (FPGA, DSP y microcontrolador) de la Figura 1 proporciona las señales de inicio de conversión ADC (CNV) y apagado del amplificador (PD) sincronizadas correctamente. El ADC de SAR inicia una conversión en el flanco ascendente de CNV. El amplificador se enciende durante la fase de adquisición de ADC durante un período de tiempo (tEN) antes del flanco ascendente de CNV, y luego se apaga sincrónicamente con el flanco ascendente de CNV. Pero, ¿cuál es el período de tiempo correcto para tEN?

Figura 3. Diagrama de tiempo simplificado para señales de control de amplificador y ADC.

Mientras que la Figura 2 ilustra el concepto usando tiempos un tanto arbitrarios para tENmuestra claramente que el valor total en DPS se realizará solo cuando el mínimo tEN se usa Este es el tiempo mínimo durante el cual el amplificador debe estar habilitado antes de la conversión ADC para garantizar un resultado preciso. Cualquier tiempo más corto que esto dará como resultado una erosión de SNR o THD, mientras que un tiempo más largo no dará como resultado ninguna mejora en el rendimiento. En la práctica, el t mínimoEN no es constante a través de las frecuencias de muestreo y debe determinarse empíricamente para la aplicación única. El mínimo tEN variará de un amplificador a otro y de un sistema a otro. Por ejemplo, usando una combinación de amplificador/ADC del ADA4805-1 y AD7980 en el circuito de la Figura 1, el mínimo tEN disminuye con el aumento de la frecuencia de muestreo, por lo general requiere ~4 μs a 1 kSPS y solo ~600 ns a 1 MSPS. A frecuencias de muestreo bajas, el período largo proporciona más tiempo para que los nodos del amplificador interno se descarguen debido a un tiempo prolongado en el estado de apagado, lo que resulta en un tiempo de encendido más largo. Por el contrario, el período más corto de frecuencias de muestreo más altas no permite tanta descarga interna. De hecho, a medida que aumenta la frecuencia de muestreo, el tiempo finito de apagado del amplificador será más largo que el tiempo invertido en el estado de apagado. En efecto, el amplificador se vuelve a encender antes de que termine de apagarse. Esto da la apariencia de un tiempo de encendido artificialmente rápido, pero se valida cuando los datos de rendimiento no muestran degradación.

Un último punto a considerar cuando se predice el ahorro potencial de energía es el efecto de la frecuencia de la señal de entrada. Hasta ahora, el concepto de DPS se ha ilustrado usando la corriente de reposo calculada de un amplificador dado. Con una señal aplicada a la entrada del amplificador, también habrá una corriente dinámica que aumenta con la frecuencia de la señal de entrada. Si la frecuencia de entrada es lo suficientemente baja, el efecto es intrascendente. A medida que aumenta la frecuencia, la red RC en la salida del amplificador presenta una carga más pesada, lo que requiere más corriente del amplificador para procesar la señal.

El uso del ADA4805-1 y el AD7980 mencionados anteriormente y la combinación de estos conceptos produce las curvas de la Figura 4. Esta figura muestra el consumo de energía, en porcentaje, del amplificador del controlador ADC escalado dinámicamente en relación con el mismo amplificador cuando está constantemente habilitado. La eficiencia DPS se traza para frecuencias de entrada seleccionadas para ilustrar el efecto de frecuencias de entrada más altas en el consumo de energía. El mínimo tEN se determinó para múltiples frecuencias de muestreo de 1 kSPS a 1 MSPS y se define como el t más cortoEN eso da como resultado una erosión de <0.5 dB en SINAD (señal a ruido y distorsión) del caso con el amplificador constantemente habilitado. La figura muestra que se pueden lograr ahorros de energía de hasta el 95 % cuando se procesan señales de entrada lentas a frecuencias de muestreo bajas. Pero lo que es más importante para los sistemas de mayor rendimiento, el ahorro potencial sigue siendo significativo, hasta un 65 % a 100 kSPS y hasta un 35 % a 1 MSPS. Es importante señalar que la figura 4 refleja el rendimiento de un solo búfer de ganancia unitaria en un sistema de muestreo continuo. Sin embargo, como se indicó anteriormente, estos conceptos de DPS se pueden aplicar fácilmente al búfer de referencia con la expectativa de resultados similares.

Figura 4. Potencia relativa del amplificador con escala de potencia dinámica: resultados experimentales.

Si bien DPS es un concepto relativamente nuevo y hay consideraciones de diseño y tiempo a tener en cuenta, los resultados iniciales son prometedores. Una cosa está muy clara, el deseo de un mayor rendimiento y un menor consumo de energía continuará en el futuro, lo que aumentará aún más la necesidad de soluciones creativas de bajo consumo.

Si quieres conocer otros artículos parecidos a Introducción al escalado dinámico de potencia puedes visitar la categoría Generalidades.

Deja una respuesta

¡Más Contenido!