Un generador de reloj de bucle doble elimina las fluctuaciones y proporciona múltiples salidas de alta frecuencia

A medida que la velocidad y la resolución de los convertidores de datos siguen aumentando, aumenta la necesidad de fuentes de reloj de frecuencia de muestreo más alta con ruido de fase más bajo. El ruido de fase incorporado (fluctuación) introducido por las entradas de reloj es uno de los cuellos de botella que enfrentan los diseñadores al crear estaciones base celulares, sistemas de radar militares y otros diseños que requieren señales de reloj de alta velocidad y alto rendimiento. Un sistema promedio tiene algunas señales ruidosas de baja frecuencia que un PLL puede convertir a una frecuencia más alta para sincronizar estos dispositivos. Un solo PLL de alta frecuencia puede resolver el problema del cambio de frecuencia, pero es difícil crear uno con un ancho de banda de bucle lo suficientemente bajo como para filtrar los efectos de la referencia ruidosa. Un PLL con un VCO/VCXO de baja frecuencia de alto rendimiento y un ancho de banda de bucle bajo puede borrar la referencia acústica, pero no puede proporcionar las salidas de alta frecuencia. El filtrado de ruido y alta velocidad se puede lograr combinando dos PLL: un dispositivo de baja frecuencia con un ancho de banda de bucle estrecho para la limpieza de fluctuaciones, seguido de un dispositivo de alta frecuencia con un ancho de banda de bucle más amplio.

Varios PLL analógicos de bucle doble modernos están integrados en un solo chip, lo que permite a los diseñadores reducir la fluctuación de referencia de baja frecuencia y proporcionar salidas de ruido de fase bajo y alta frecuencia. Esto ahorra un área valiosa de PCB y permite sincronizar múltiples dispositivos que requieren diferentes frecuencias desde una fuente alineada de fase única.

Los generadores de reloj AD9523, AD9523-1 y AD9524, que se muestran en la Figura 1, constan de dos PLL analógicos conectados en serie. El primer PLL (PLL1) elimina la fluctuación de fase de referencia y el segundo PLL (PLL2) genera salidas de alta frecuencia alineadas en fase. PLL2 puede generar una frecuencia base alta a partir de la cual se pueden derivar varias frecuencias más bajas. PLL1 utiliza un VCXO externo de baja frecuencia y un filtro de bucle de tercer orden parcialmente integrado para crear un PLL con un ancho de banda de bucle en el rango de 30 Hz a 100 Hz. El ancho de banda de este bucle afecta directamente la cantidad de ruido de una etapa de entrada de referencia que se propagará a la salida. PLL2 utiliza un VCO interno de alta velocidad sintonizado a 3,8 GHz (3 GHz para el AD9523-1) y un filtro de bucle de tercer orden parcialmente integrado para darle un ancho de banda de bucle nominal de alrededor de 500 kHz. El ancho de banda y el ruido de fase de este VCO interno afectan directamente el ruido de banda ancha de fase de la salida total.

Muchos ingenieros piensan en los PLL de doble lazo como convertidores de frecuencia que reducen la fluctuación de la entrada de referencia en una cantidad fija, pero es más exacto pensar en ellos como convertidores de frecuencia de bajo ruido de fase cuyo rendimiento se ve afectado por el ancho de banda y la fase de cada PLL. perfiles de ruido de VCOs/VCXOs.

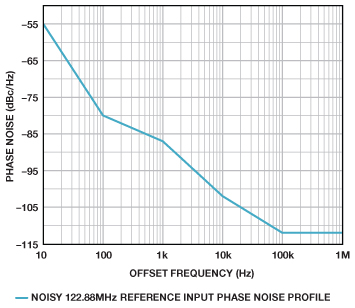

El ADisimCLK™ La herramienta de simulación proporciona una forma sencilla de determinar los efectos del ruido de fase de referencia en el ruido de fase de salida de un PLL de bucle doble. Este ejemplo utiliza ADIsimCLK para modelar los efectos de una referencia acústica en el ruido de fase general del AD9523-1. La figura 2 muestra una referencia simulada a 122,88 MHz con un perfil de ruido de fase típico.

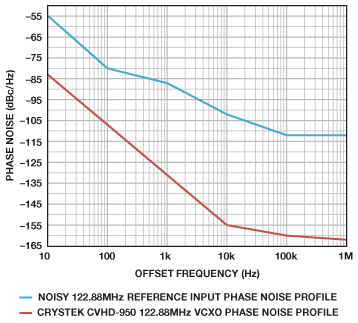

PLL1 se basa en un VCXO de alto rendimiento y un ancho de banda de bucle bajo para atenuar el ruido de fase de referencia, lo que permite que domine el ruido de fase del VCXO. Este ejemplo utiliza un Crystek CVHD-950 VCXO para generar una frecuencia de salida igual a la entrada de referencia. Esto muestra una comparación directa de la cantidad de ruido de fase de referencia visto en la salida de PLL1. La Figura 3 compara el perfil de ruido de fase del Crystek CVHD-950 VCXO con el ruido de fase de entrada de referencia.

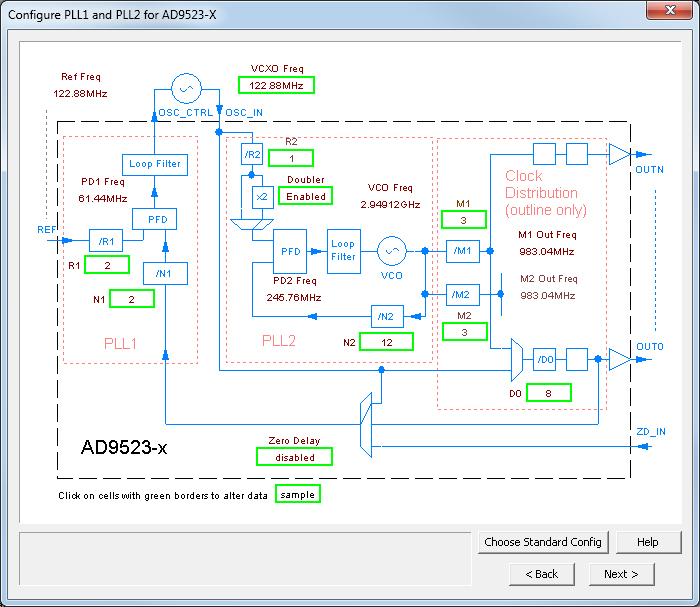

La Figura 4 y la Tabla 1 muestran los parámetros de configuración de ADIsimCLK utilizados para simular la respuesta de ruido de la etapa de salida PLL1 del AD9523-1 a la entrada de referencia y los perfiles de ruido de la etapa PLL1 VCXO que se muestran en la Figura 3. La Tabla 2 muestra los valores del filtro de bucle PLL1 generado por ADIsimCLK dada esta configuración.

Tabla 1. Parámetros de configuración de PLL1

| Variable | Haz una evaluación |

| Frecuencia de operación VCXO | 122,88 MHz |

| Frecuencia de referencia | 122,88 MHz |

| Frecuencia de salida | 122,88 MHz |

| compartidor electrónico | 2 |

| Partícipe | 2 |

| corriente de la bomba de carga | 6 µA |

| kVCO Crystek CVHD-950 | 3,07 kHz/V |

| Ancho de banda de bucle deseado | 30 Hz |

| Margen de grado deseado | 75° |

Tabla 2. Valores del componente de filtro de bucle PLL1 generados por ADIsimCLK

| Variable | Haz una evaluación |

| contraPOLÍTICA1 | 1.5nF |

| Rcero | 10kΩ |

| contraEXT | 4,7 µF |

| RPOLÍTICA2 | 165kΩ |

| contraPOLÍTICA2 | 337 pF |

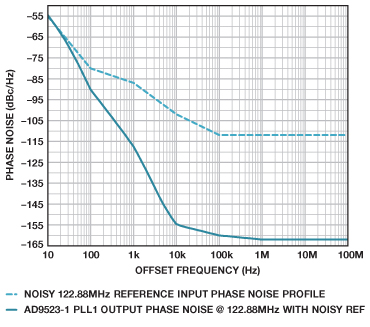

La figura 5 muestra la salida simulada de PLL1 a 122,88 MHz (línea continua) de ADIsimCLK junto con el perfil de ruido de la fase base de la referencia acústica de 122,88 MHz (línea discontinua). Tenga en cuenta que el ruido de fase de salida del PLL1 es mucho menor que el ruido de fase de entrada de referencia original. El ancho de banda del bucle PLL1 reduce en gran medida el ruido de fase de referencia, lo que permite que el perfil de ruido de fase baja del VCXO domine la frecuencia de corte del bucle de 30 Hz. el ruido solo aumentará en función del ancho de banda del bucle PLL1.

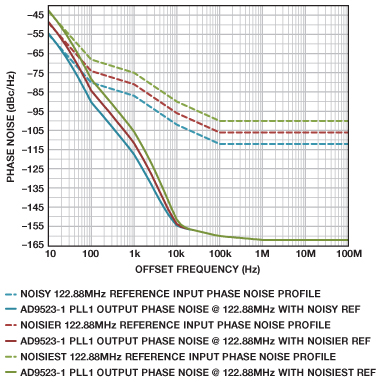

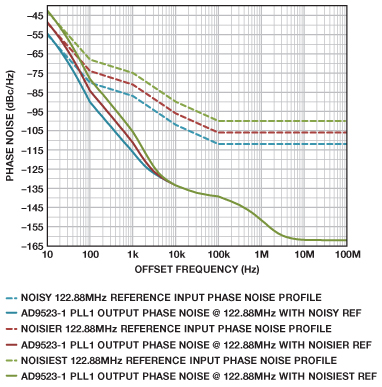

La Figura 6 y la Figura 7 muestran la salida PLL1 del AD9523-1 con un ruido de fase de 6 dB y 12 dB más alto que la referencia ruidosa que se muestra en la Figura 2. Más allá de una frecuencia de compensación de aproximadamente 20 kHz, el ruido de fase de salida del PLL1 está dominado por su parámetros de bucle y el rendimiento del VCXO. Por lo tanto, con un rango de integración que comienza con un desplazamiento de 20 kHz, el rendimiento de Jitter cambiará solo ligeramente, a pesar del aumento de 12 dB en el ruido de fase de entrada de referencia. Este es un resultado directo del diseño de PLL1 para tener un ancho de banda de bucle bajo y usar un VCXO de bajo ruido de fase. VCXO de baja frecuencia de alto rendimiento con bajo KVCO Debe usarse para crear un ancho de banda de bucle PLL1 lo suficientemente pequeño para realizar esta limpieza. La salida de ruido de fase baja de PLL1 ahora sirve como referencia para que PLL2 alinee una salida de frecuencia más alta para crear una fase.

PLL2 tiene un VCO interno sintonizado a 3 GHz para permitir frecuencias de salida de hasta 1 GHz. Para comparar la referencia de entrada de ruido con el ruido de fase general de la familia AD9523, examine el ruido de fase resultante a 122,88 MHz (FVCO dividido por 24). Tenga en cuenta que las salidas PLL2 generalmente se usan para traducción de frecuencia o salidas de alta frecuencia. La Tabla 3 muestra los parámetros de configuración de PLL2 ingresados en ADIsimCLK. La Tabla 4 muestra los valores del filtro de bucle PLL2 generados por ADIsimCLK dada esta configuración.

Tabla 3. Parámetros de configuración de PLL2

| Variable | Haz una evaluación |

| Frecuencia de funcionamiento del VCO | 2949,12 MHz |

| Frecuencia de referencia PLL1 | 122,88 MHz |

| Doble habilitado? | Sí |

| Frecuencia de salida | 122,88 MHz |

| compartidor electrónico | 1 |

| Partícipe | 12 |

| separador M1 | 3 |

| divisor de salida | 8 |

| corriente de la bomba de carga | 417 µA |

| Ancho de banda de bucle deseado | 450 Hz |

| Margen de grado deseado | 70° |

Tabla 4. Valores de los componentes del filtro de bucle ADIsimCLK PLL2

| Variable | Haz una evaluación |

| contraPOLÍTICA1 | 16pF |

| Rcero | 1.85kΩ |

| contraEXT | 1.2nF |

| RPOLÍTICA2 | 900Ω |

| contraPOLÍTICA2 | 16pF |

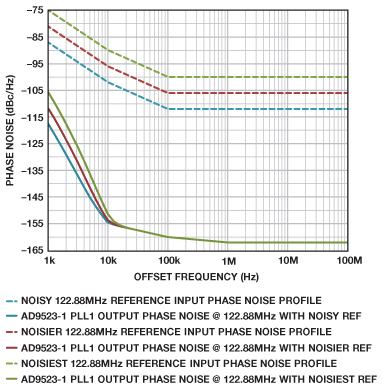

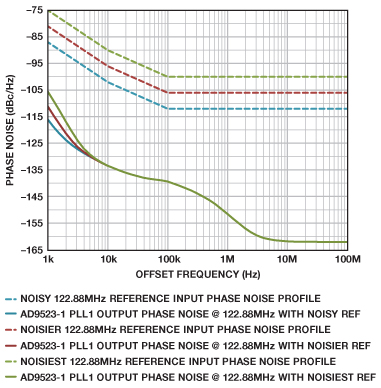

La Figura 8 y la Figura 9 comparan el ruido de la etapa de entrada de referencia y el ruido de la etapa de salida resultante del AD9523-1 simulado con ADisimCLK. Tenga en cuenta que hay un nivel de ruido adicional entre 10 kHz y 1 MHz. Esto se debe al ruido de fase interno del VCO de PLL2.

El ruido de fase interno del VCO en PLL2 es lo suficientemente alto después de una frecuencia de compensación de aproximadamente 5 kHz que comienza a afectar significativamente el ruido de fase de salida general del dispositivo. El ruido de la etapa de referencia adicional tiene un efecto mínimo sobre el ruido de la etapa de salida después de la región de compensación de 5 kHz.

Conclusión

La función de limpieza Jitter de PLL1 evita que la mayor parte del ruido de la etapa de entrada de referencia llegue a PLL2. El ruido cercano a la fase (compensación de menos de 10 kHz) se ve afectado por una entrada de referencia ruidosa, pero la fluctuación de la salida del dispositivo en lugar del rendimiento de referencia es mayor. En los casos en los que la fluctuación de fase integrada se calcula entre 12 kHz y 20 MHz, es probable que la fluctuación de fase de salida sea la misma independientemente de la fluctuación de fase de entrada. En lugar de afirmar cuánto jitter puede mitigar un PLL analógico de bucle doble, la medida real del rendimiento debería ser la cantidad de jitter que genera.

Si quieres conocer otros artículos parecidos a Un generador de reloj de bucle doble elimina las fluctuaciones y proporciona múltiples salidas de alta frecuencia puedes visitar la categoría Generalidades.

Deja una respuesta

¡Más Contenido!