Pipelining: Arquitectura, ventajas y desventajas

El aumento de la velocidad de ejecución del programa aumenta en consecuencia la velocidad del procesador. Se han inventado muchas formas, tanto de implementación de hardware como de arquitectura de software, para aumentar la velocidad de ejecución. Se ha observado que ejecutando las instrucciones de forma concurrente se puede reducir el tiempo de ejecución. Se propuso el concepto de paralelismo en la programación. Según éste, se puede ejecutar más de una instrucción por ciclo de reloj. Este concepto puede ser practicado por un programador mediante diversas técnicas como Pipelining, unidades de ejecución múltiples y núcleos múltiples. Entre todos estos métodos de paralelismo, el pipelining es el más practicado. Entonces, ¿cómo se puede ejecutar una instrucción en el método de pipelining? ¿Cómo aumenta la velocidad de ejecución?

¿Qué es el pipelining?

Para comprender el concepto de pipelining, veamos el nivel raíz de cómo se ejecuta el programa. La instrucción es el paquete de ejecución más pequeño de un programa. Cada instrucción contiene una o varias operaciones. Los procesadores escalares simples ejecutan una o más instrucciones por ciclo de reloj, y cada instrucción contiene sólo una operación. Las instrucciones se ejecutan como una secuencia de fases, para producir los resultados esperados. Esta secuencia es la siguiente

- SI: Recoge la instrucción en el registro de instrucciones.

- ID: Decodificación de la instrucción, decodifica la instrucción para el opcode.

- AG: Generador de direcciones, genera la dirección.

- DF: Recuperación de datos, recupera los operandos en el registro de datos.

- EX: Ejecución, ejecuta la operación especificada.

- WB: Reescribir, escribe el resultado en el registro.

No todas las instrucciones requieren todos los pasos anteriores, pero la mayoría sí. Estos pasos utilizan diferentes funciones de hardware. En el pipelining estas diferentes fases se realizan de forma concurrente. En el pipelining estas fases se consideran independientes entre las distintas operaciones y pueden solaparse. Así, se pueden realizar varias operaciones simultáneamente, estando cada una de ellas en su propia fase independiente.

Canalización de instrucciones

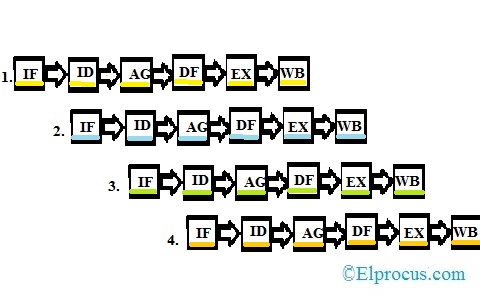

Veamos cómo se procesan las instrucciones en el pipelining. Esto se puede entender fácilmente con el siguiente diagrama.

Supongamos que las instrucciones son independientes. En un procesador de pipelining simple, en un momento dado, sólo hay una operación en cada fase. La fase inicial es la fase IF. Por tanto, en el primer ciclo de reloj, se obtiene una operación. Cuando llega el siguiente pulso de reloj, la primera operación pasa a la fase ID, dejando la fase IF vacía. Ahora, esta fase vacía se asigna a la siguiente operación. Así, durante el segundo pulso de reloj, la primera operación está en la fase ID y la segunda en la fase IF.

En el tercer ciclo, la primera operación estará en la fase AG, la segunda en la fase ID y la tercera en la fase IF. De este modo, las instrucciones se ejecutan de forma concurrente y, tras seis ciclos, el procesador emitirá una instrucción completamente ejecutada por ciclo de reloj.

Si esta instrucción se ejecuta secuencialmente, inicialmente la primera instrucción tiene que pasar por todas las fases y luego se obtiene la siguiente instrucción Entonces, para la ejecución de cada instrucción, el procesador necesitaría seis ciclos de reloj. Pero en un procesador canalizado, como la ejecución de las instrucciones tiene lugar de forma concurrente, sólo la instrucción inicial requiere seis ciclos y todas las instrucciones restantes se ejecutan como una por cada ciclo, reduciendo así el tiempo de ejecución y aumentando la velocidad del procesador.

Arquitectura Pipelining

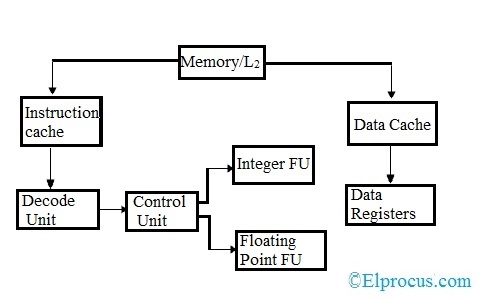

El paralelismo se puede conseguir con técnicas de hardware, compilador y software. Para explotar el concepto de pipelining en la arquitectura de los ordenadores, se interconectan muchas unidades de procesamiento que funcionan simultáneamente. En la arquitectura de procesadores en tuberías, hay unidades de procesamiento separadas para las instrucciones de números enteros y de punto flotante. Mientras que en la arquitectura secuencial, se proporciona una única unidad funcional.

En la canalización estática, el procesador debe hacer pasar la instrucción por todas las fases de la canalización, independientemente del requisito de la instrucción. En un procesador de canalización dinámica, una instrucción puede eludir las fases en función de su necesidad, pero tiene que moverse en orden secuencial. En un procesador de pipeline dinámico complejo, la instrucción puede saltarse las fases, así como elegir las fases fuera de orden.

Pipelining en los procesadores RISC

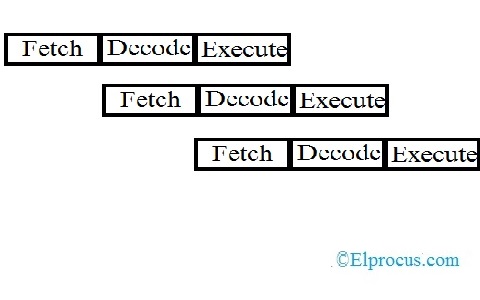

El procesador ARM de arquitectura RISC más popular sigue un pipelining de 3 y 5 etapas. En el pipelining de 3 etapas, las etapas son: Captación, Descodificación y Ejecución. Este pipelining tiene una latencia de 3 ciclos, ya que una instrucción individual tarda 3 ciclos de reloj en completarse.

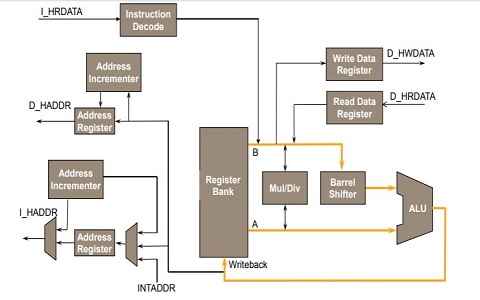

Para una correcta implementación del pipelining también hay que actualizar la arquitectura de hardware. El hardware para el pipelining de 3 etapas incluye un banco de registros, una ALU, un cambiador de barril, un generador de direcciones, un incrementador, un decodificador de instrucciones y registros de datos.

En el pipelining de 5 etapas las etapas son: Búsqueda, Descodificación, Ejecución, Buffer/datos y Escritura.

Peligros del pipelining

En un programa informático típico, además de las instrucciones simples, hay instrucciones de bifurcación, operaciones de interrupción, instrucciones de lectura y escritura. El pipelining no es adecuado para todo tipo de instrucciones. Cuando algunas instrucciones se ejecutan en pipelining, pueden paralizar el pipeline o vaciarlo totalmente. Este tipo de problemas causados durante el pipelining se llama Peligros del Pipelining.

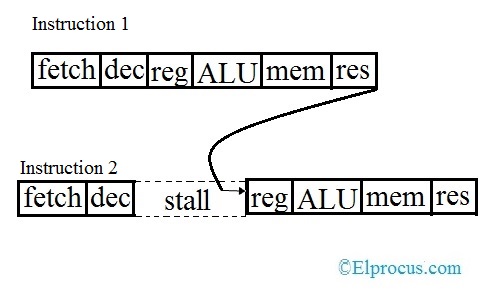

En la mayoría de los programas informáticos, el resultado de una instrucción se utiliza como operando de otra instrucción. Cuando estas instrucciones se ejecutan en pipelining, se produce un fallo, ya que el resultado de la primera instrucción no está disponible cuando la segunda instrucción empieza a recoger operandos. Por lo tanto, la instrucción dos debe detenerse hasta que se ejecute la instrucción uno y se genere el resultado. Este tipo de riesgo se denomina riesgo de canalización de lectura después de la escritura.

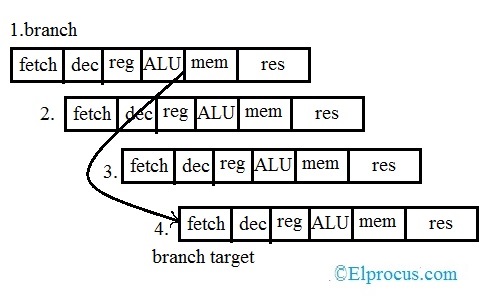

La ejecución de instrucciones de bifurcación también provoca un peligro de canalización. Las instrucciones de bifurcación mientras se ejecutan en pipelining afecta a las etapas de búsqueda de las siguientes instrucciones.

Ventajas del pipelining

- El rendimiento de las instrucciones aumenta.

- El aumento del número de etapas del pipeline aumenta el número de instrucciones ejecutadas simultáneamente.

- Se puede diseñar una ALU más rápida cuando se utiliza el pipelining.

- Las CPUs con pipelining trabajan a frecuencias de reloj más altas que la RAM.

- La canalización aumenta el rendimiento general de la CPU.

Desventajas del pipelining

- El diseño del procesador con pipelines es complejo.

- La latencia de las instrucciones aumenta en los procesadores con canalización.

- El rendimiento de un procesador en cadena es difícil de predecir.

- Cuanto más larga sea la tubería, peor será el problema del peligro para las instrucciones de bifurcación.

La canalización beneficia a todas las instrucciones que siguen una secuencia de pasos similar para su ejecución. Los procesadores que tienen instrucciones complejas en las que cada instrucción se comporta de forma diferente a las demás son difíciles de canalizar. Los procesadores tienen implementaciones razonables con 3 o 5 etapas del pipeline porque a medida que aumenta la profundidad del pipeline aumentan los peligros relacionados con él. ¿Nombra algunos de los procesadores con pipeline con su etapa de pipeline?

Si quieres conocer otros artículos parecidos a Pipelining: Arquitectura, ventajas y desventajas puedes visitar la categoría Generalidades.

Deja una respuesta

¡Más Contenido!